# A Very Low Loss 220–325 GHz Silicon Micromachined Waveguide Technology

Bernhard Beuerle, James Campion, Umer Shah and Joachim Oberhammer

Abstract—This paper reports for the first time on a very low loss silicon micromachined waveguide technology, implemented for the frequency band of 220 - 325 GHz. The waveguide is realized by utilizing a double H-plane split in a three-wafer stack. This ensures very low surface roughness, in particular on the top and bottom surfaces of the waveguide, without the use of any surface roughness reduction processing steps. This is superior to previous micromachined waveguide concepts, including E-plane and single H-plane split waveguides. The measured average surface roughness is 2.14 nm for the top/bottom of the waveguide, and 163.13 nm for the waveguide sidewalls. The measured insertion loss per unit length is 0.02 - 0.07 dB/mm for 220 - 325 GHz, with a gold layer thickness of 1 µm on the top/bottom and 0.3 µm on the sidewalls. This represents, in this frequency band, the lowest loss for any silicon micromachined waveguide published to date and is of the same order as the best metal waveguides.

Index Terms—RF MEMS, micromachined waveguide, rectangular waveguide, submillimeter-wave, terahertz

# I. INTRODUCTION

The low insertion loss of rectangular waveguides, in particular when compared to planar transmission lines, makes them the ideal transmission medium for millimeter and submillimeter wave frequencies. Waveguide insertion loss depends on the surface roughness of the waveguide walls and the type and thickness of surface metallization. For split-block waveguides, the split geometry and joining technique also influence the insertion loss. CNC milling of metal split-blocks is the most established method to fabricate rectangular waveguides. The resulting milled surfaces have too high nonuniformity to allow for proper bonding of the split blocks. Low loss metal waveguides are therefore almost exclusively implemented in an E-plane split design, as this provides the lowest loss if the split cannot be ideally bonded together. Moreover, this design allows for relatively straightforward coupling to active devices using E-field probes [1]. An insertion loss of 0.20 - 0.25 dB/mm has been reported for aluminium splitblock waveguides [2] in the WR-3.4 band, whereas a noncommercial gold electroplated split-block WR-3.7 waveguide achieved an insertion loss of 0.015 dB/mm [3]. By comparison, an insertion loss of 1.6 dB/mm for co-planar waveguides (CPW) on GaAs and 2.5 dB/mm for coplanar striplines on sapphire at 300 GHz have been reported [4]. Microstrip lines using BCB as dielectric achieve an insertion loss of 0.88 dB/mm at 330 GHz [5].

The authors are with the Department of Micro and Nanosystems, School of Electrical Engineering and Computer Science, KTH Royal Institute of Technology, Stockholm SE-100 44, Sweden (e-mail: beuerle@kth.se).

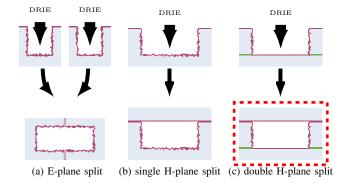

Fig. 1. Micromachined waveguide surface roughness: (a) E-plane split, waveguide halves DRIE along the waveguide width and subsequently joined together [6], [7]; (b) single H-plane split DRIE along the waveguide height [8], [6], [9]; and (c) double H-plane split DRIE along the waveguide height, as proposed in this paper.

Fig. 2. Fabrication process: (a) bare SOI wafer; (b) waveguide structure after DRIE silicon etch and subsequent removal of the buried oxide layer; and (c) metallization using sputtering and (d) final waveguide after thermocompression bonding.

Micromachining offers a number of advantages for the fabrication of waveguide components, which become particularly beneficial when approaching terahertz frequencies. The ability to implement small feature sizes with accurate tolerances allows for the integration of components of complex geometries [10]. These accurate tolerances, when combined with volume batch processing, result in high product uniformity and low fabrication costs. Micromachining also makes it possible to achieve low surface roughness and near ideal metallic bonding, reducing the insertion loss of a waveguide and allowing for the use of H-plane split designs. H-plane split waveguides are less sensitive to misalignment than E-plane split waveguides, simplifying waveguide assembly.

Insertion loss as low as 0.03 dB/mm has been shown for WR-3.4 micromachined waveguides using thick SU-8, either directly metallized or used as molds for electroplating [11]. However, it is difficult to apply SU-8 uniformly and stabilize it. Therefore, deep reactive-ion etching (DRIE) of trenches in silicon with subsequent metallization is the most common fabrication technique for micromachined waveguides. For

1

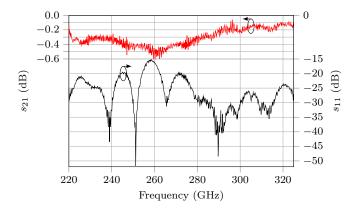

Fig. 3. Measured transmission and reflection coefficient of a waveguide line with a length of  $l=7.1\,\mathrm{mm}$ .

$500-750\,\mathrm{GHz}$ , the reported insertion loss for E-plane and H-plane split micromachined waveguides is  $0.08-0.12\,\mathrm{dB/mm}$  and  $0.06-0.12\,\mathrm{dB/mm}$ , respectively [6]. In [7] an additional oxidation and etch-back step was added to decrease the surface roughness, reducing the insertion loss for an E-plane split waveguide to  $0.05-0.07\,\mathrm{dB/mm}$ .

The DRIE process for an E-plane split waveguide results in high surface roughness on all four waveguide walls. The roughness of the sidewalls is particularly high since this is the bottom surface during DRIE (Fig. 1a). Single H-plane split waveguides are fabricated by etching the waveguide recess into a silicon wafer and bonding a cap wafer on top (Fig. 1b). Here, the cap wafer is not etched and therefore has a surface roughness of a few nanometers, but all three other walls are etched and contribute to the insertion loss.

In this paper we present, for the first time, a silicon micromachined WR-3.4 waveguide utilizing a double H-plane split (Fig. 1c). The proposed technique drastically reduces the overall surface roughness, resulting in the lowest insertion loss reported to date for any silicon micromachined waveguide in this frequency band.

## II. DESIGN AND FABRICATION

The implemented waveguide has the standard WR-3.4 waveguide width of 864 µm but a reduced height of 275 µm. The waveguide technology consists of a metallized three-wafer stack with two H-plane splits: (1) the handle layer of a siliconon-insulator (SOI) wafer into which the waveguide channel is etched; (2) its device layer acting as the bottom of the waveguide; and (3) a silicon cap wafer as the top of the waveguide. The height of the waveguide can be controlled down to micrometer tolerances, since it is defined by the thickness of the SOI handle layer. Unlike for a single H-plane split, both the bottom and the top surface of the waveguide in this design have a surface roughness of a few nanometers, even after metallization. Furthermore, the surface roughness of the etched sidewalls is significantly lower than that of an E-plane split micromachined waveguide as the etch depth is significantly smaller (36% in our design).

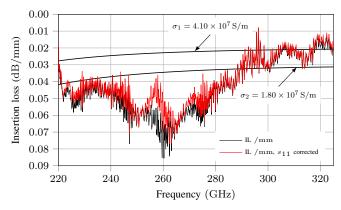

Fig. 4. Measured insertion loss and  $s_{11}$  corrected insertion loss per unit length of a waveguide line with a length of  $l=7.1\,\mathrm{mm}$ , compared to the theoretical waveguide losses for a gold plated waveguide with an ideal conductivity of  $\sigma_1=4.1\times10^7\,\mathrm{S/m}$  and a reduced conductivity of  $\sigma_2=1.8\times10^7\,\mathrm{S/m}$ , which provides a close fit to the measured data.

The main steps of the fabrication process are illustrated in Fig. 2. The handle layer of the SOI wafer is etched using deep reactive ion etching with a three-step Bosch process (Fig. 2b). The SOI buried oxide (BOX) layer acts as an etch stop and is subsequently removed by plasma etching. Both the SOI wafer and the silicon cap wafer are then metallized with 1.0  $\mu$ m of gold (waveguide top and bottom) using sputter deposition (Fig. 2c), resulting in a thickness of 0.3  $\mu$ m on the waveguide sidewalls. Finally, the individual chips are bonded using thermo-compression bonding at 200 °C (Fig. 2d).

# III. CHARACTERIZATION

To measure the scattering parameters and determine the insertion loss per unit length of the waveguide technology, a waveguide line with a length of 7.1 mm has been fabricated. This waveguide is characterized using a Rohde & Schwarz ZVA 24 Vector Network Analyzer with two Rohde & Schwarz ZC330 TxRx extension heads over the frequency band of 220 – 325 GHz. A micromachined on-chip Thru-Reflect-Line calibration kit is used to move the reference planes to the waveguide ports. The measured transmission and reflection coefficients for the waveguide line are shown in Fig. 3.

The measured insertion loss of the waveguide line is better than  $0.6\,\mathrm{dB}$  across the band. Except for a single  $15\,\mathrm{dB}$  peak, the return loss is better than  $20\,\mathrm{dB}$ . The measured insertion loss per unit length is shown in Fig. 4, with and without correction by the measured return loss. It is between  $0.02-0.07\,\mathrm{dB/mm}$ , averaging  $0.039\,\mathrm{dB/mm}$ . The theoretical waveguide loss per unit length for a WR-3.4 waveguide with an ideal conductivity of  $\sigma_1=4.1\times10^7\,\mathrm{S/m}$  is plotted as reference. Assuming a conductivity of  $\sigma_2=1.8\times10^7\,\mathrm{S/m}$  the theoretical loss gives a close fit to the measured data.

As a reference, a commercially available gold-metallized E-plane split waveguide has been characterized with the same setup, with a measured insertion loss of  $0.02-0.025\,\mathrm{dB/mm}$  in the frequency band of  $280-330\,\mathrm{GHz}$ , which is of the order of values reported in the literature (Table I).

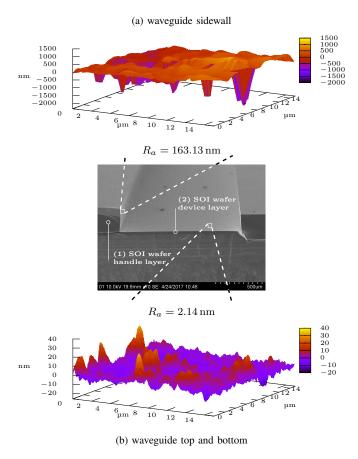

Fig. 5. Cross-sectional SEM image, unbonded waveguide after gold deposition: (1) SOI wafer handle layer (waveguide sidewalls); and (2) SOI wafer device layer (waveguide top and bottom). The measured average surface roughness (RMS) of the waveguide walls is (a)  $R_a=163.13\,\mathrm{nm}$  for the waveguide sidewall; and (b)  $R_a=2.14\,\mathrm{nm}$  for the waveguide bottom.

Assuming the same surface roughness for a WR-1.5 waveguide implemented in this technology without an additional oxidation step, the loss per unit length for the waveguide with conductivity  $\sigma_2=1.8\times10^7$  S/m is expected to be between 0.07 dB/mm and 0.10 dB/mm for the frequency band of 500 – 750 GHz.

Fig. 5 shows a scanning electron microscope (SEM) image of a cross-section of the waveguide after gold deposition. The surface roughness was measured with an optical profilometer over a  $15\,\mu\mathrm{m}\times15\,\mu\mathrm{m}$  area. The measured average surface roughness (RMS) is 2.14 nm for the waveguide top/bottom (Fig. 5a) and 163.13 nm for the waveguide sidewalls (Fig. 5b).

The low insertion loss of the waveguide was achieved without an additional oxidation step (as was used in [7]) and is attributed to its design (Section II). The state of the art performance for different fabrication techniques is summarized in Table I.

### IV. CONCLUSION

A double H-plane split silicon micromachined waveguide technology has been presented for the first time and implemented for the frequency band of  $220-325\,\text{GHz}$ . The measured insertion loss of the waveguide is  $0.02-0.07\,\text{dB/mm}$  over the whole frequency band, with an average of  $0.039\,\text{dB/mm}$ ,

Table I STATE OF THE ART WAVEGUIDE TECHNOLOGIES

| Reference          | Technology                    | Split  | h (nm)                | f (GHz)               | Loss (dB/mm)                |

|--------------------|-------------------------------|--------|-----------------------|-----------------------|-----------------------------|

| [2]                | CNC, Al                       | E      |                       | 325 – 360             | 0.20 - 0.25                 |

| [2]<br>[12]<br>[3] | CNC, Au plated CNC, Au plated | E<br>E | _                     | 220 - 330 $210 - 280$ | 0.03 - 0.06 $0.014 - 0.018$ |

| [11]               | SU-8                          | Е      | _                     | 220 - 325             | 0.03 - 0.05                 |

| [8]                | DRIE                          | Н      | 75 <sup>1</sup>       | 500 - 700             | 0.10 - 0.20                 |

| [6]                | DRIE                          | E      | $110^{-2}$            | 500 - 750             | 0.08 - 0.12                 |

| [6]                | DRIE                          | H      | 20 / 110 <sup>3</sup> | 500 - 750             | 0.06 - 0.12                 |

| [7]                | DRIE, ox. step                | E      | 43 4                  | 500 - 750             | 0.05 - 0.07                 |

| This work          | DRIE double-                  | Н      | 2 / 160 <sup>5</sup>  | 220 – 325             | 0.02 - 0.07                 |

- 1 measured sidewall scallops

- <sup>2</sup> RMS

- 3 RMS top / bottom and sidewall roughness

- <sup>4</sup> RMS, 199 nm before surface roughness reducing oxidation step

- <sup>5</sup> RMS top and bottom / sidewall roughness, without any oxidation step

without the use of additional surface roughness reduction methods. This represents, to the best of our knowledge, the lowest loss silicon micromachined waveguide in this frequency band to date.

#### ACKNOWLEDGEMENT

The contribution by KTH to this work has received funding from the European Research Council (ERC) under the European Union's Horizon 2020 research and innovation programme (grant agreement No. 616846) and the Swedish Foundation for Strategic Research Synergy Grant Electronics SE13-007.

## REFERENCES

- K. Eriksson, P. J. Sobis et al., "InP DHBT Amplifier Modules Operating Between 150-300 GHz Using Membrane Technology," *IEEE Transactions on Microwave Theory and Techniques*, vol. 63, no. 2, pp. 433–440, Feb 2015.

- [2] T. Reck, C. Jung-Kubiak et al., "A Silicon Micromachined Eight-Pixel Transceiver Array for Submillimeter-Wave Radar," *IEEE Transactions* on *Terahertz Science and Technology*, vol. 5, no. 2, pp. 197–206, Mar 2015.

- [3] A. R. Kerr, C. Litton et al., Loss of Gold Plated Waveguides at 210-280 GHz, ALMA, Jan 2009, ALMA Memo 585.

- GHz, ALMA, Jan 2009, ALMA Memo 585.

[4] M. Frankel, S. Gupta et al., "Terahertz Attenuation and Dispersion Characteristics of Coplanar Transmission Lines," *IEEE Transactions on Microwave Theory and Techniques*, vol. 39, no. 6, pp. 910–916, Jun 1991.

- [5] J. Hacker, M. Urteaga et al., "250 nm InP DHBT Monolithic Amplifiers with 4.8 dB Gain at 324 GHz," in 2008 IEEE MTT-S International Microwave Symposium Digest. IEEE, Jun 2008.

- [6] T. Reck, C. Jung-Kubiak et al., "Measurement of Silicon Micromachined Waveguide Components at 500-750 GHz," *IEEE Transactions on Tera*hertz Science and Technology, vol. 4, no. 1, pp. 33–38, Jan 2014.

- [7] C. Jung-Kubiak, T. J. Reck et al., "A Multistep DRIE Process for Complex Terahertz Waveguide Components," *IEEE Transactions on Terahertz Science and Technology*, vol. 6, no. 5, pp. 690–695, Sept 2016.

- [8] K. M. K. H. Leong, K. Hennig et al., "WR1.5 Silicon Micromachined Waveguide Components and Active Circuit Integration Methodology," *IEEE Transactions on Microwave Theory and Techniques*, vol. 60, no. 4, pp. 998–1005, Apr 2012.

- [9] M. Vahidpour and K. Sarabandi, "2.5D Micromachined 240 GHz Cavity-Backed Coplanar Waveguide to Rectangular Waveguide Transition," IEEE Transactions on Terahertz Science and Technology, vol. 2, no. 3, pp. 315–322, May 2012.

- [10] U. Shah, T. Reck et al., "A 500-750 GHz RF MEMS Waveguide Switch," IEEE Transactions on Terahertz Science and Technology, vol. 7, no. 3, pp. 326–334, May 2017.

- pp. 326–334, May 2017.

[11] X. Shang, M. Ke et al., "WR-3 Band Waveguides and Filters Fabricated Using SU8 Photoresist Micromachining Technology," *IEEE Transactions on Terahertz Science and Technology*, vol. 2, no. 6, pp. 629–637, Nov 2012.

- [12] J.-Q. Ding, S.-C. Shi et al., "WR-3 Band Quasi-Elliptical Waveguide Filters Using Higher Order Mode Resonances," IEEE Transactions on Terahertz Science and Technology, vol. 7, no. 3, pp. 302–309, May 2017.