#### **Asynchronous sequence circuits**

- An asynchronous sequence machine is a sequence circuit without flip-flops

- Asynchronous sequence machines are based on combinational gates with feedback

# <u>Upon analysis it is assumed</u>: Only one signal at a time in the gate circuit can change its value at any time

#### Golden rule

# Asynchronous state machine

Asynchronous state machines are used when it is necessary to maintain a state, but when there is no clock available.

- All flip-flops and latches are themselfes asynchronous state machines

- They are useful to synchronize events in situations where metastability is/can be a problem

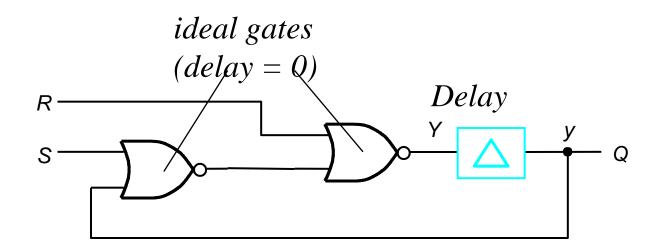

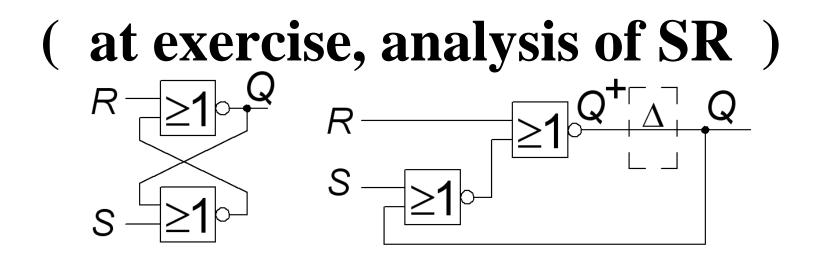

## **SR-latch with NOR-gates**

To analyze the behavior of an asynchronous circuit one assumes ideal gates and summarizes all the delay to a single block with delay  $\Delta$ .

# **Analysis of sequence circuits**

#### By having a **delay block** we can consider

- y as the present state

- **Y** as next state

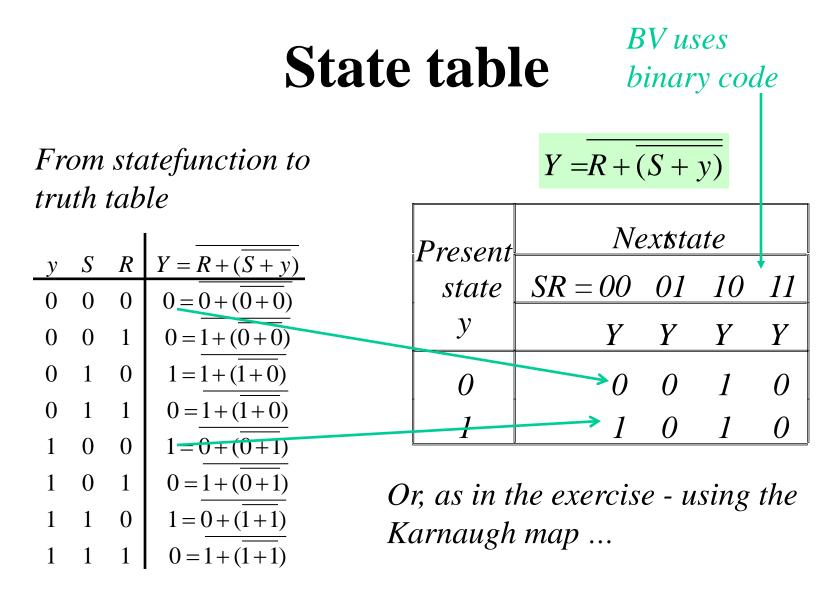

#### State function

Thus, we can develop a functional relationship of the next state Y depending on the input signals Sand R and the current state y

$$Y = R + \overline{(S + y)}$$

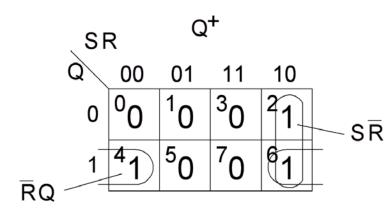

$$Q^{+} = \overline{R + \overline{S + Q}} = \overline{R} \cdot \overline{\overline{(S + Q)}} = \overline{R} \cdot (S + Q) = S\overline{R} + \overline{R}Q$$

| Present | Next state Q <sup>+</sup> |    |    |    |  |  |  |

|---------|---------------------------|----|----|----|--|--|--|

| state Q | Input signals SR          |    |    |    |  |  |  |

|         | 00                        | 01 | 11 | 10 |  |  |  |

| 0       | 0                         | 0  | 0  | 1  |  |  |  |

| 1       | 1                         | 0  | 0  | 1  |  |  |  |

For binary order

| Present | Nextstate |    |    |    |  |  |  |  |

|---------|-----------|----|----|----|--|--|--|--|

| state   | SR = 00   | 01 | 10 | 11 |  |  |  |  |

| У       | Y         | Y  | Y  | Y  |  |  |  |  |

| 0       | 0         | 0  | 1  | 0  |  |  |  |  |

| 1       | 1         | 0  | 1  | 0  |  |  |  |  |

- Since we do not have flip-flops, but only combinational circuits, a state change can result in additional state changes

- A state is

- stable if  $Y(t) = y(t + \Delta)$

- unstable if  $Y(t) \neq y(t + \Delta)$

$$Y = y$$

stable

### **Exitation table**

The asynchronous coded state table is calledExcitation table

The stable states (those with next state = present state) will be "encircled"

| Present | Ne         |            |            |            |         |

|---------|------------|------------|------------|------------|---------|

|         | SR = 00    | 01         | 10         | 11         |         |

| У       | Y          | Y          | Y          | Y          |         |

| 0       | $\bigcirc$ | $\bigcirc$ | 1          | $\bigcirc$ | (Y = y) |

| 1       |            | 0          | $\bigcirc$ | 0          |         |

# Terminology

When dealing with asynchronous sequential circuits a different terminology is used

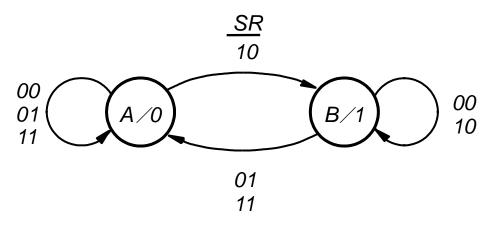

• The asynchronous uncoded state table is called **flow table**

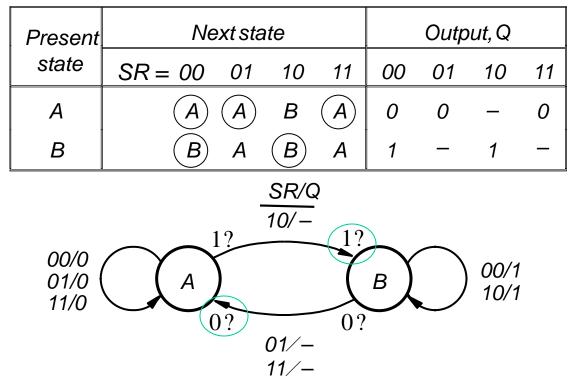

# Flowtable and Statediagram (Moore type)

| Present | Next state                                  | Output |

|---------|---------------------------------------------|--------|

| state   | SR = 00  01  10  11                         | Q      |

| A       | (A) (A) B (A)                               | 0      |

| В       | $\bigcirc B \land \land \bigcirc B \land A$ | 1      |

William Sandqvist william@kth.se

## Flowtable and Statediagram (Mealy type)

Don't care ('-') has been selected for the output decoder. It does not matter if the output is changed before or after the state transition (= simpler gate array).

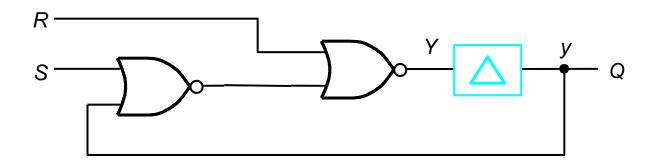

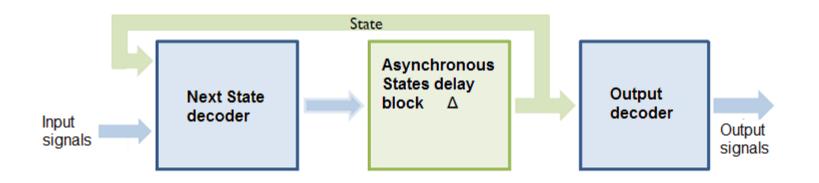

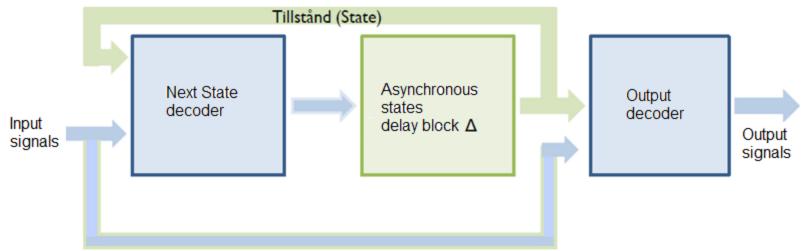

# Asynchronous Moore compatible

- Asynchronous sequential circuits have similar structure as synchronous sequential circuits

- Instead of flip-flops one have a "delay block"

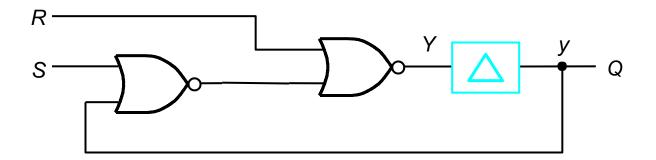

# Asynchronous Mealy compatible

- Asynchronous sequential circuits have similar structure as synchronous sequential circuits

- Instead of flip-flops one have a "delay block"

#### Analysis of asynchronous circuits

#### The analysis is done in the following steps :

- 1) Replace the feedbacks in the circuit with delay element

- $\Delta_i$ . Input signal to delay-element forms the next state  $Y_i$ , while the output signal  $y_i$  represents the present state.

- 2) Find out the next-state and output expressions

- 3) Set up the corresponding excitationstable

- 4) Create a flow table by replacing the encoded states by symbolic states

- 5) Draw a state diagram if needed

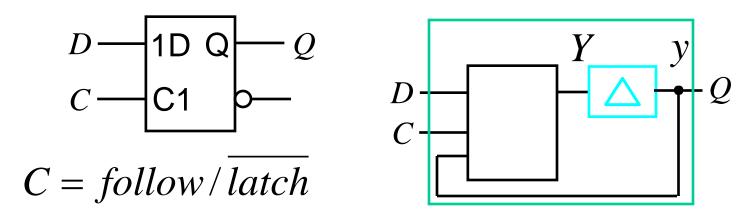

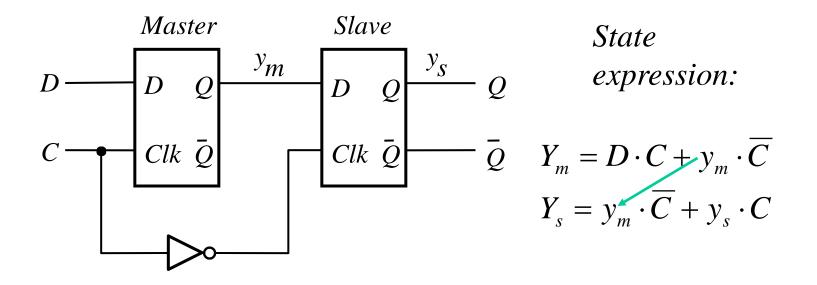

#### **First: D-latch state function**

D-latch statefunction. Functional relationship between the current state *y* and next state *Y*

$$Y = D \cdot C + y \cdot C$$

$$\uparrow \qquad \uparrow$$

follow  $\overline{latch}$

#### **Exemple: Master-Slave-flip-flop**

Master-slave D flip-flop is constructed from two asynchronous D-latches.

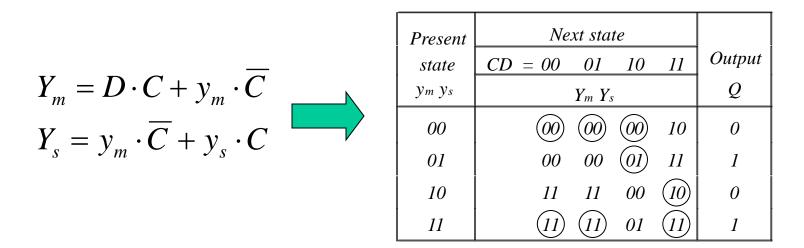

#### Exitationstable

From the expressions one can directly derive the excitation table (if you can keep it all in your head?)

## or with help from K-map ...

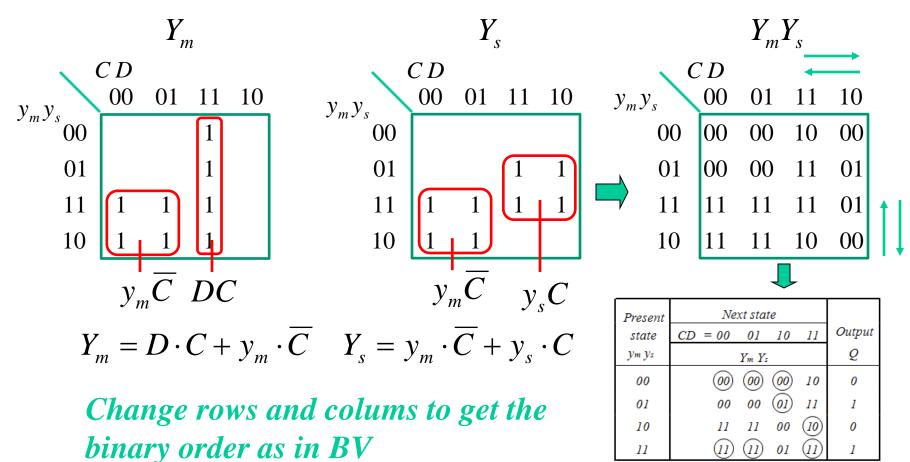

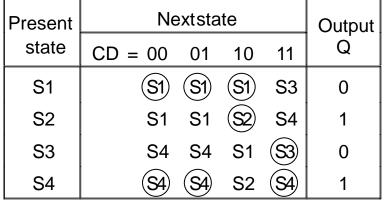

#### **Flow table**

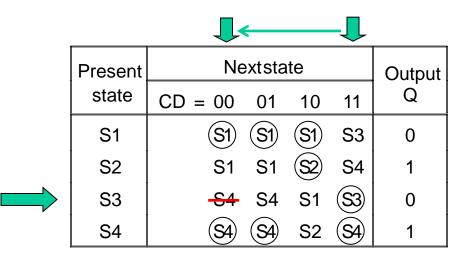

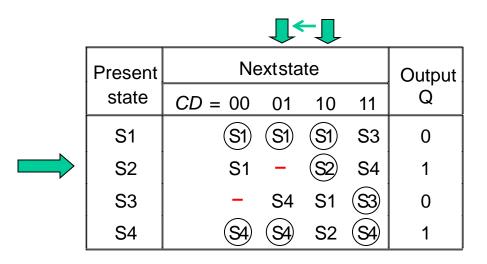

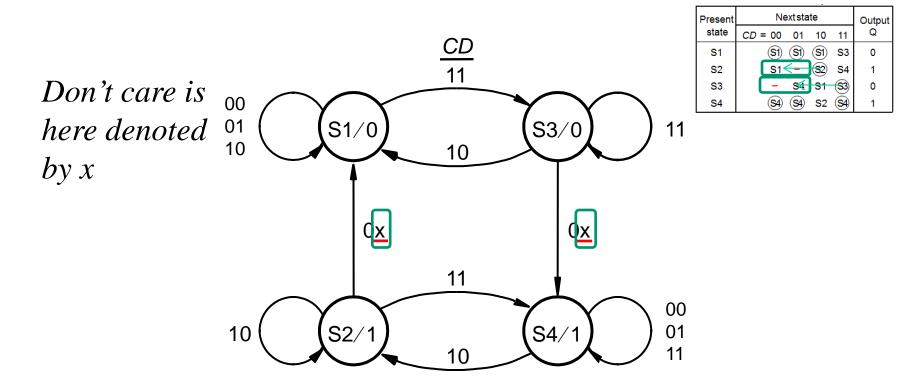

We define four states S1, S2, S3, S4, which gives us the flow table

|                  | Mustatuta                                             |        | l | Present | Ne       | extsta   | ate      |          | Output |

|------------------|-------------------------------------------------------|--------|---|---------|----------|----------|----------|----------|--------|

| Present<br>state | Next state<br>CD = 00 01 10 11                        | Output |   | state   | CD = 00  | 01       | 10       | 11       | Q      |

| Ym Ys            | Ym Ys                                                 | Q      |   | S1      | (S1)     | (S1)     | (S1)     | S3       | 0      |

| 00               | $\bigcirc \bigcirc \bigcirc \bigcirc \bigcirc 0 0 10$ | 0      |   |         |          | U        | $\simeq$ |          |        |

| 01               | 00 00 (01) 11                                         | 1      |   | S2      | S1       | S1       | (S2)     | S4       | 1      |

| 10               | 11 11 00 (10)                                         | 0      |   | S3      | S4       | S4       | S1       | (S3)     | 0      |

| 11               | (1) (1) 01 (1)                                        | 1      |   |         | $\frown$ | $\frown$ |          | $\simeq$ |        |

|                  |                                                       |        | - | S4      | (54)     | (S4)     | S2       | (S4)     | 1      |

#### Flow table

**Remember**: Only one input can be changed at a time

• *Thus, some transitions will never be able to happen!*

#### Flowtable – impossible transitions

#### State S3

Only stable state for S3 is when input is 11

Only one input at a time can change  $\rightarrow$  possible changes are  $11 \rightarrow 01$ ,

$11 \rightarrow 10$

- Theese combinations leaves S3!

- Input 00 in S3 is *not* possible!

- Input 00 is therefore **don't care**!

#### Flowtable – impossible transitions

#### State S2

Only stable state for S2 is when input is 10

Only one input at a time can change  $\rightarrow$  possible changes are  $10 \rightarrow 11, 10$

$\rightarrow 00$

- Theese combinations leave S2!

- Input 01 in S2 is *not* possible!

- Input 01 is therefore **don't care**!

#### **D-flip-flop state diagram**

Don't care can be used to simplify the circuit (the next state decoder).

#### Synthesis of asynchronous circuits

# The synthesis is carried out in the following steps :

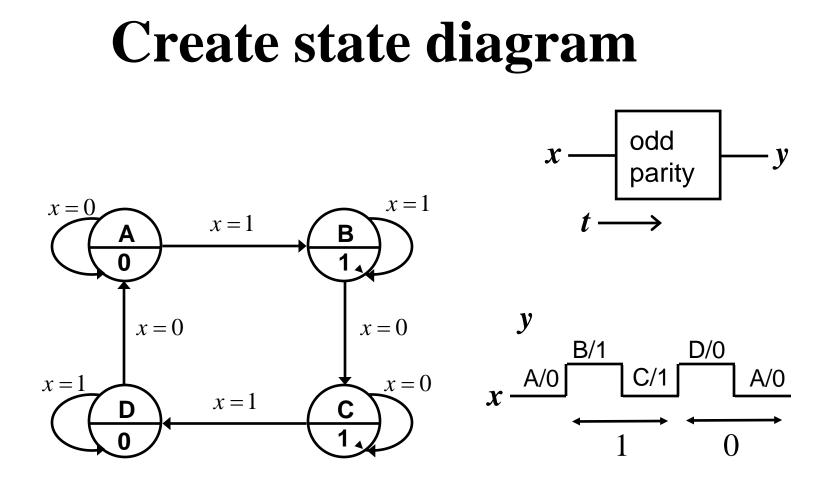

1) Create a **state diagram** acording to the functional description

2) Create a flow table and reduce the number of states if possible

3) Assign codes to the states and create the **excitationstable**

4) Develop expressions (transfer functions) for next state and outputs

5) Design a circuit that implements the above expressions

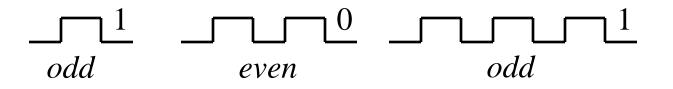

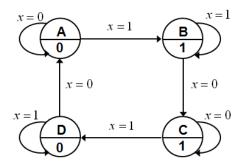

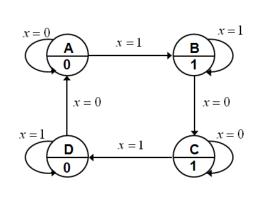

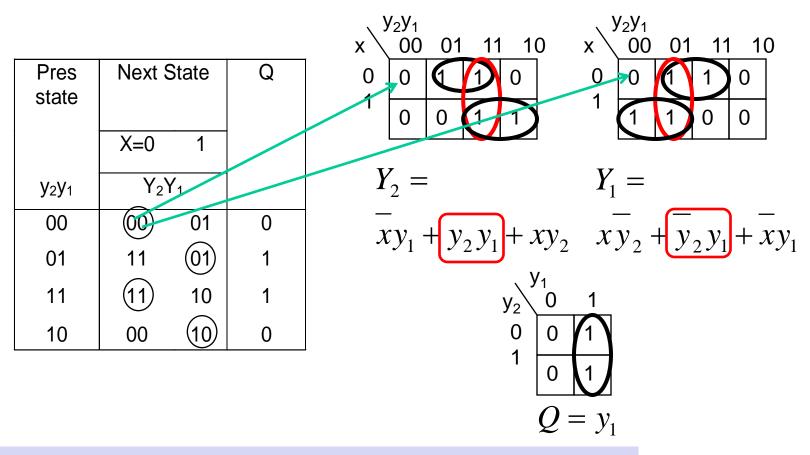

## **Exemple: serial paritety circuit**

Input x Output y x = 0 odd y = 1 if the number of pulses at  $t \to t$ input x is an odd number.

In other words, an "every other time" circuit ...

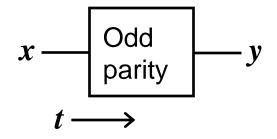

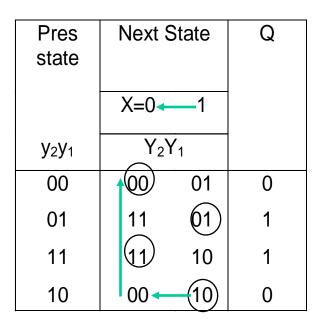

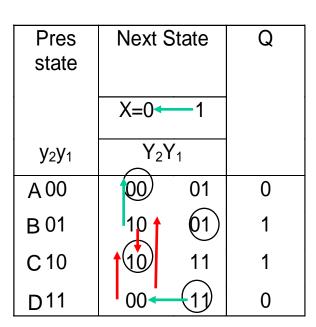

#### **Create state table**

| Pres<br>state | Next S     | Q          |   |

|---------------|------------|------------|---|

|               | X=0        | 1          |   |

| A             | (A)        | В          | 0 |

| В             | C          | B          | 1 |

| С             | <b>(C)</b> | D          | 1 |

| D             | Α          | $\bigcirc$ | 0 |

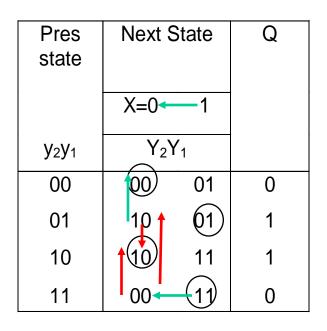

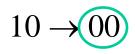

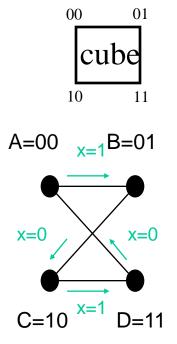

#### What is a good state encoding? 00, 01, 10, 11 - binary code?

• Suppose X = 1  $Y_2Y_1 = 11$ • Then  $X \rightarrow 0 \rightarrow Y_2Y_1 = 00?$   $11 \rightarrow 10!$  $11 \rightarrow 01 \rightarrow 10!$   $? \rightarrow 00$

Bad encoding (HD=2!)

We will never reach 00?

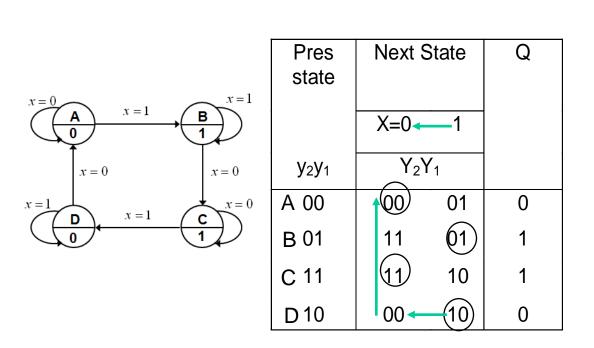

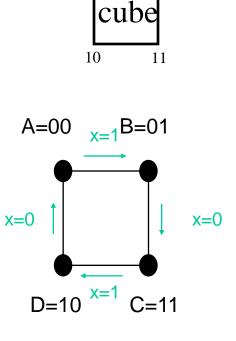

#### What is a good state encoding? 00, 01, 11, 10 – gray code

• Suppose X = 1  $Y_2Y_1 = 10$ • Then  $X \rightarrow 0 \rightarrow Y_2Y_1 = 00$

Good encoding (HD=1)

# **State encoding**

- In asynchronous sequential circuits, *Richard Hamming* it is impossible to guarantee that the two state variables changes values simultaneously

- Thus, a transition  $00 \rightarrow 11$  could result in

- A transition  $00 \rightarrow 01 \rightarrow ???$

- A transition  $00 \rightarrow 10 \rightarrow ???$

- To ensure the function all state transitions <u>MUST</u> have the *Hamming distans* 1

- The Hamming distans is the number of bits that differs in two binary numbers

- Hamming distans between 00 and 11 is 2

- Hamming distans between 00 and 01 is 1

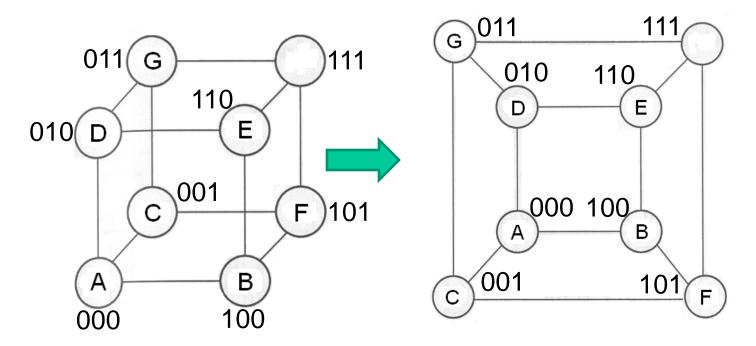

# **Good state encoding**

• Procedure to obtain good codes:

1) Draw the transition diagram along the edges in hypercubes (Gray code) formed by the codes

- 2) Remove any crossing lines by

- a) change the position of two adjacent nodes

- b) utilize available unused codes (exploit unstable conditions)

- c) introduce hypercube of more dimensions

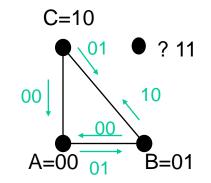

#### Poor coding of the parity circuit

The poor state encoding

Poor encoding – Hamming Distance = 2 ( **crossing lines** )

#### Good coding of the parity circuit

The good state encoding

00

01

Good encoding Hamming Distance = 1 (**no crossing lines**)

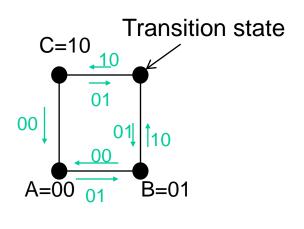

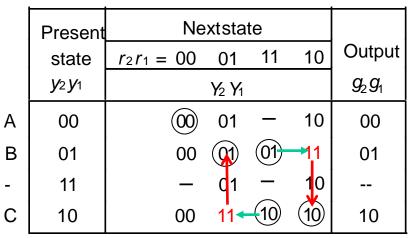

#### **Problems with non-stable states**

#### Ex. an other circuit:

| Present | Nextstate     |    |            |            | Output    |

|---------|---------------|----|------------|------------|-----------|

| state   | $r_2r_1 = 00$ | 01 | 10         | 11         | $g_2 g_1$ |

| A 00    | A             | В  | С          | Ι          | 00        |

| B 01    | A             | B  | С          | B          | 01        |

| C 10    | А             | В  | $\bigcirc$ | $\bigcirc$ | 10        |

#### Bad encoding

At the transition between **B** to **C** (or **C** to **B**) is the Hamming distans 2  $(10\leftrightarrow 01)!$ Chance to get stuck in an unspecified state (with the code 11)!

#### Solution to unstable state

• Solution: The introduction of a transition state that ensure that you do not end up in an undefined state!

Good encoding

$\begin{array}{c} 01 \rightarrow 11 \rightarrow 10 \\ 10 \rightarrow 11 \rightarrow 01 \\ \hline \\ Transition state \end{array}$

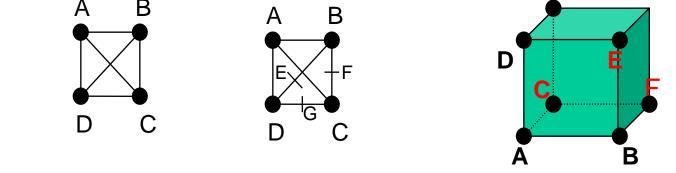

#### **Extra states – more dimensions**

One can increase the number of dimensions in order to implement secure state transitions

A B A B

If there is no way redraw the chart to HD = 1 you may add states by increasing the dimension of the hypercube. You then drag the transitions through the then available non-stable states.

#### **Extra states – more dimensions**

• It's easier to draw a "flat" 3D cube (perspective, is then from the front)

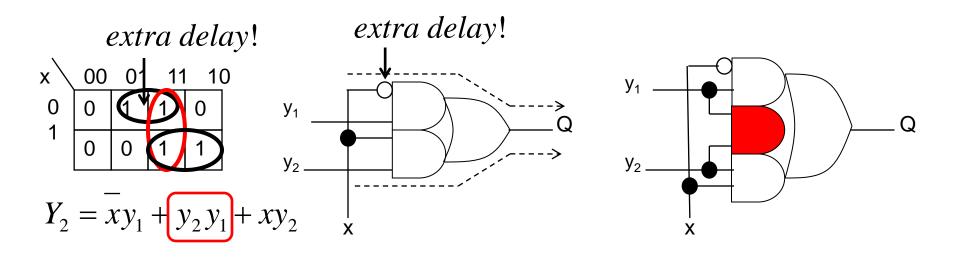

## **Karnaugh maps**

Groupings in red are to avoid Hazard (see later in course)!

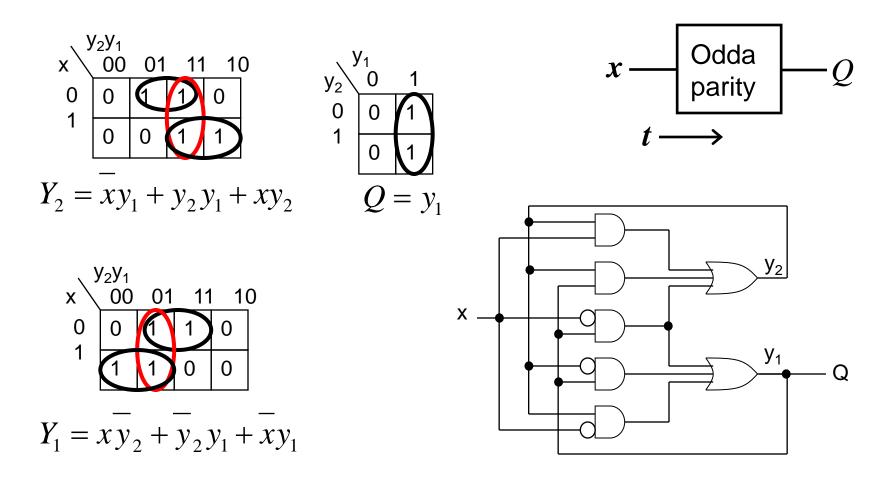

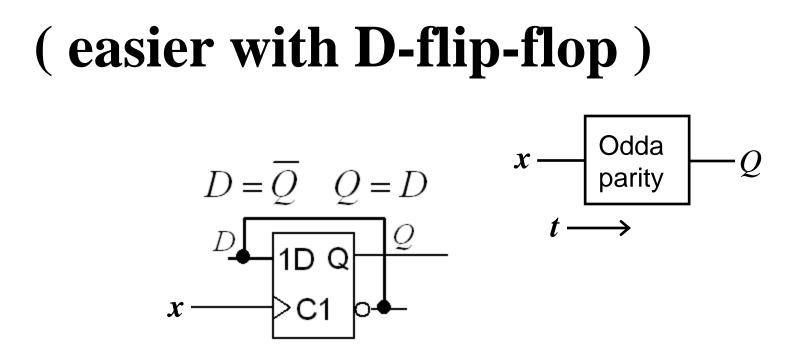

## The complete circuit

We have made an ''every other time'' earlier in the course. Then with a D flip-flop. But now it was more exiting!

# What is Hazard?

- Hazard is a term that means that there is a danger that the output is not stable, but it may "flicker" at certain input combinations.

- Hazard occurs if there is a different distance from the various inputs to an output, there will be an signal-race.

- In order to counteract this, one must add the prime implikants to cover up the dangerous transition.

# **Exemple of Hazard – MUX**

At the transition from  $xy_2y_1=(111) \rightarrow (011)$  the output Q could *flicker*, because the road from x to Q are longer via the upper AND-gate than the lower (race).

#### MORE ABOUT HAZARD IN THE NEXT LECTURE!

Asynchronous state machines has many "unspecified" positions in the flow table that can be exploited to minimize the number of states.

The probability that less number of states leads to a simpler implementation is high in the case of asynchronous circuits!

Two steps:

**Equivalency -** equivalent state. The same steps as the state minimization of synchronous sequential circuits, full flexibility remain.

**Compatibility -** compatible states will be different for Moore or Mealy compliant realization, the choices you make now affect the future flexibility.

#### • Procedure for minimizing the number of states

- Forming equivalence groups.

To be in the same group, the following shall apply:

- Outputs must have the same value

- Stable states must be in the same place (column)

- Don't cares for next state muste be at the same place (column)

- 2. Minimize equivalence groups (state-reduction)

- 3. Form **merger diagram** different for Mealy or Moore.

- 4. Merge compatible states in groups. Minimize the number of groups simultaneously. Each state may only be part of one group.

- 5. Construct the reduced flow table by merging rows in the selected groups

- 6. Repeat step 3-5 to see if more minimizations may be done

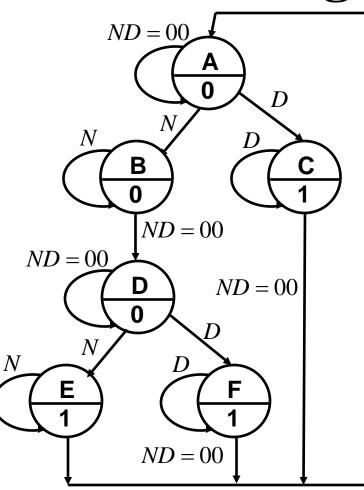

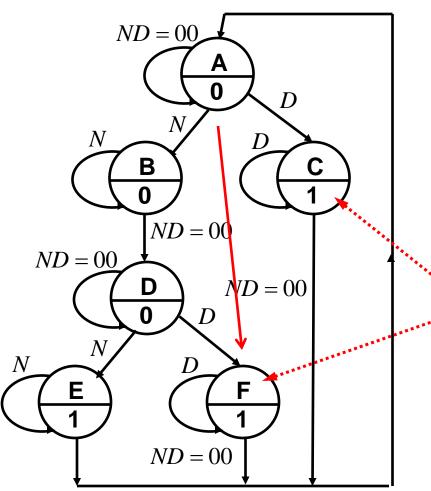

# Candy Machine (BV p. 610)

- Candy Machine has two inputs:

- N: Nickel (5 cent)

- **D**: Dime (10 cent)

- A candy costs 10 cent

- The machine does not return any money if there are 15 cent in the machine ( one candy is returned )

- Output *z* is active when there is enough money for a candy

# State diagram, Flow table

- No "double changes" of input signals!

- You can't insert two coins at the same time!

(X = ND, Q = z)

A flow table that only has one stable state on each row is called a *primitive flowtable*.

State Minimization means that two states may be equivalent, and if so, replaced by one state to simplify the state diagram, and network.

One can easily see that state C and F could be replaced by one state, as a candy always be ejected after a Dime regardless of previous state.

# Form/minimize equivalence groups

- **1. Form equivalence groups.** To be in the same group, the following applies:

- Outputs must have the same value

- Stable states must be at same place (column)

- Don't cares for next state must be at same place (column)

- 2. Minimize equivalence groups (state reduction).

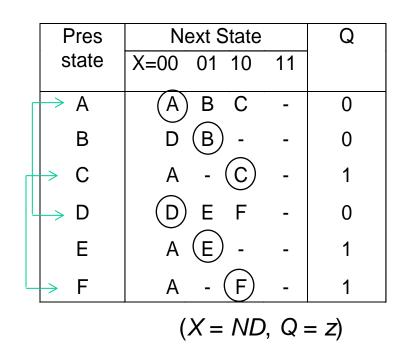

## • Equivalence groups

The states is divided in blocks after the output value.

**ABD** has output **0**, **CEF** has output **1**.  $P_1 = (ABD)(CEF)$

Stable states must be for same input signal (column), don't care must be for same column.

**AD** has a stable state for 00. **B** has a stable for 01. **CF** has a stable state for 10. **E** has a stable for 01. **AD** and **CF** has don't care for corresponding input signals.

$P_2 = (AD)(B)(CF)(E)$

#### Merge equivalence groups

Two rows could be "merged" if it does not conflikt their successor states

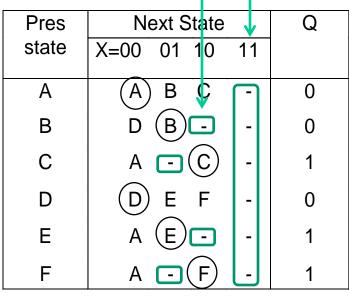

| Pres            | Next State |    | Q |

|-----------------|------------|----|---|

| state           | X=00 01 10 | 11 |   |

|                 |            |    |   |

| A               | (A) B C    | -  | 0 |

| В               | DB-        | -  | 0 |

| С               | A - C      | -  | 1 |

| D               | DEF        | -  | 0 |

| E               | ĀĒ.        | -  | 1 |

| F               | A - (F)    | -  | 1 |

| (X = ND, Q = z) |            |    |   |

$P_2=(AD)(B)(CF)(E)$   $P_3=(A)(D)(B)(C)(E)$  $P_4=P_3$ . Rows **C** and **F** can be merged with a new name **C**, while **A** and **D** which has successors in different groups *not* can merge.

| $C, F_{00} \rightarrow (AD), (AD)$               | Resulting flow table |               |   |  |

|--------------------------------------------------|----------------------|---------------|---|--|

| $C,F_{01} \rightarrow -, -$                      | Pres                 | Next State    | Q |  |

| $C,F_{10} \rightarrow (CF), (CF)$                | state                | X=00 01 10 11 |   |  |

| $C,F_{11} \rightarrow -, -$                      | A                    | (A) B C -     | 0 |  |

|                                                  | В                    | D (B)         | 0 |  |

| $A, D_{00} \rightarrow (AD), (AD)$               | C                    | A - C -       | 1 |  |

| $A,D_{01} \rightarrow (\mathbf{B}),(\mathbf{E})$ | D                    | DEC-          | 0 |  |

| $A, D_{10} \rightarrow (CF), (CF)$               | E                    | A (E)         | 1 |  |

| $A, D_{11} \rightarrow -, -$                     |                      |               |   |  |

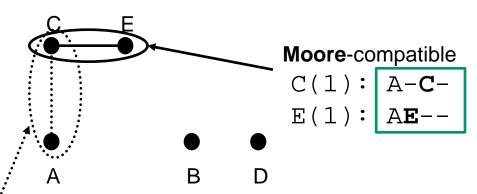

# **Compatibility Groups**

- 3. Form merger charts **either** for **Mealy** or **Moore**

- 4. Merge compatible states into groups. Minimize the number of groups simultaneously. Each state may only be part of a group.

- 5. Construct the reduced flow table by merging rows in the selected groups

- 6. Repeat steps 3-5 to see if more minimizations can be done

# Merging rules

- Two states are "compatible", and can be merged if the following applies

- 1. at least one of the following conditions apply to all input combinations

- both S<sub>i</sub> and S<sub>i</sub> has the same successor state, or

- both S<sub>i</sub> and S<sub>j</sub> are stable, or

- The successor to  $S_i$  or  $S_j$  are both unspecified

- 2. Then if you want to construct a Moore-compatible statemachine it also apply

- both S<sub>i</sub> and S<sub>j</sub> has the same **output value** ( this is not necessary when you construct a Mealy-compatible statemachine)

# Merger diagram

**Resulting flowtable**

|          | Pres         | Next State |     |    |    | Q |

|----------|--------------|------------|-----|----|----|---|

|          | state        | X=00       | 01  | 10 | 11 |   |

|          | A            | A          | B   | С  | -  | 0 |

|          | В            | D          | (B) | -  | -  | 0 |

| <b>_</b> | L <b>⇒</b> C | A          |     | C  | -  | 1 |

|          | D            |            | Е   | С  | -  | 0 |

| L        | →E           | А          | E   | -  | -  | 1 |

• When there are there are several possibilities ...

Compatibily graph

Each line will be a point in the Compatibility graph.

**Mealy**-compatible: In state **A** (X = 00) the output is 0, in state **C** output is 1

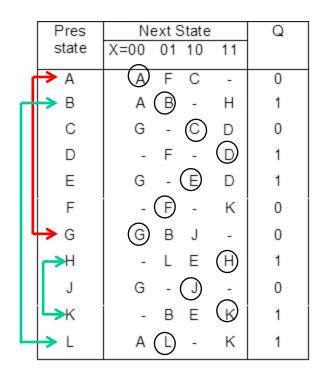

## An illustrative example (BV 9.8)

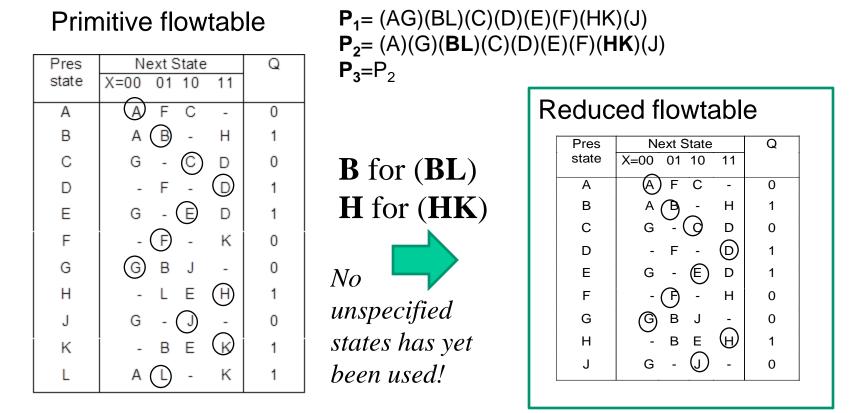

**Primitive flowtable**

equivalence classes

The same output, same position for stable states and do not care conditions (AG) (BL) (HK)

$\mathbf{P}_1$ = (AG)(BL)(C)(D)(E)(F)(HK)(J)

Successor state: A, G are *not* equivalent  $A,G_{00} \rightarrow (AG), (AG) \quad A,G_{01} \rightarrow (F), (BL)$   $A,G_{10} \rightarrow (C), (J) \quad A,G_{11} \rightarrow -, B,L_{00} \rightarrow (AG), (AG) \quad B,L_{01} \rightarrow (BL), (BL)$   $B,L_{10} \rightarrow -, - \quad B,L_{11} \rightarrow (HK), (HK)$   $H,K_{00} \rightarrow -, - \quad H,K_{01} \rightarrow (BL), (BL)$   $H,K_{10} \rightarrow (E), (E) \quad H,K_{11} \rightarrow (HK), (HK)$  $P_2= (A)(G)(BL)(C)(D)(E)(F)(HK)(J) \quad P_3=P_2$

## An illustrative example (BV 9.8)

#### equivalence classes

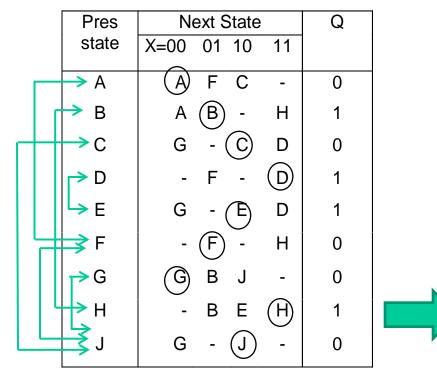

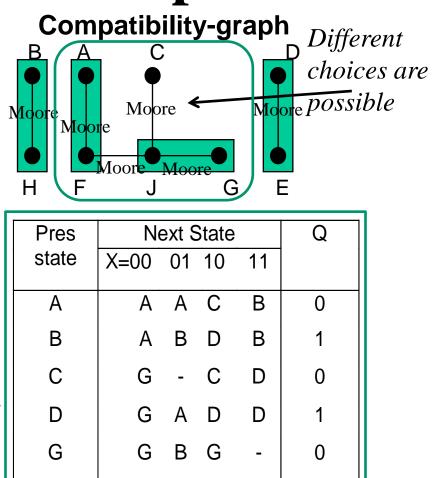

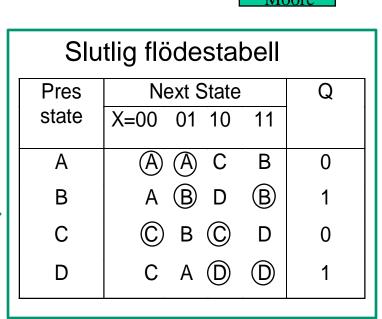

# An illustrative example ... Compatibility Compatibility-graph <sub>Г</sub>

Reduced flowtable

New names **B** (**BH**), **A** (**AF**), **G** (**JG**), **D** (**DE**) William

#### An illustrative example ... Compatibility-graph

В

Α

More reduced flowtable

Next State Pres Q state X=00 01 10 11 (A)С А В 0 (A)B B B Α D 1  $\bigcirc$ С G D 0 (D) $\bigcirc$ G 1 D А В G G G 0

D

G

New name C for (CG)

Now all the unspecified conditions are used!

# Summary

- Asynchronous state machines

- Based on analysis of feedback combinational networks

- All flip-flops and latches are asynchronous state machines

- A similar theory as for synchronous state machines can be applied

- Only one input or state variable can be changed at a time!

- One must also take into account the race problem