# Written reexam for IE1204/5 Digital Design Monday 14/3 2016 14.00-18.00

#### General Information

Examiner: Ingo Sander.

Teacher: William Sandqvist phone 08-7904487

Exam text does not have to be returned when you hand in your writing.

Aids: No aids are allowed!

The exam consists of three parts with a total of 14 tasks, and a total of 30 points:

**Part A1** (**Analysis**) containes ten short questions. Right answer will give you one point. Incorrect answer will give you zero points. The total number of points in Part A1 is 10 points. To pass the **Part A1** requires at least 6p, if fewer points we will not look at the rest of your exam.

Part A2 (Methods) contains two method problems on a total of 10 points.

To **pass the exam** requires at least **11 points** from A1 + A2, if fewer points we will not look at the rest of your exam.

**Part B (Design problems)** contains two design problems of a total of 10 points. Part B is corrected only if there are at **least 11p** from the exam A- Part.

**NOTE!** At the end of the exam text there is a submission sheet for Part A1, which shall be separated and be submitted together with the solutions for A2 and B.

For a passing grade (**E**) requires at **least 11 points on the exam**. If exactly 10p A1(6p)+A2(4p), (FX), completion to (E) will be offered.

**Grades** are given as follows:

| 0 – | 11 – | 16 – | 19 – | 22 – | 25 |

|-----|------|------|------|------|----|

| F   | Е    | D    | C    | В    | A  |

The result is expected to be announced before Monday 4/4 2016.

## Part A1: Analysis

Only answers are needed in Part A1. Write the answers on the submission sheet for Part A1, which can be found at the end of the exam text.

#### **1.** 1p/0p

A function f(x, y, z) is described by the expression:

$$f(x, y, z) = (\overline{z \oplus x})(\overline{x} + \overline{z})(\overline{xyz})$$

Write down the function as a **minimized** product of sums, **PoS**.

$$f(x, y, z) = \{PoS\}_{min} = ?$$

#### **2.** 1p/0p

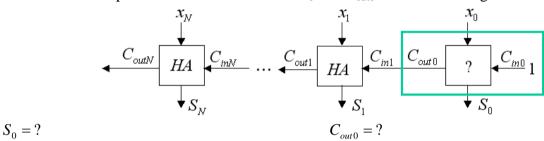

A special case of addition is when a binary number  $x(x_N...x_1x_0)$  is incremented with 1, S = x + 1. One can then build a simplified adder as in the figure. Since there is one number and not two numbers being added it is enough to use half adders (HA) instead of full adders (FA). The first stage can be further simplified. Derive the functions  $S_0$  and  $C_{\text{out}0}$  for this first stage.

#### **3.** 1p/0p

Two two-complement 4 bit binary numbers are x = 1010 and y = 0011. Give the result of the **multiplication**  $x \cdot y$  as a two-complement 8-bit binary number (sign extended to 8 bit).

#### **4**. 1p/0p

Given is a Karnaugh map for a function of four variables  $Y = f(x_3, x_2, x_1, x_0)$ . Write the function as a minimized  $Y_{min}$  sum of products, on **SoP** form. "-" in the map means "don't care".

| $x_3x_2$ | × <sub>0</sub> | 01             | 11              | 10                    |

|----------|----------------|----------------|-----------------|-----------------------|

| 00       | 0_             | <sup>1</sup> 1 | <sup>3</sup> 1  | <sup>2</sup> <b>0</b> |

| 01       | <sup>4</sup> 0 | 5,             | <sup>7</sup> 1  | <sup>6</sup> 1        |

| 11       | 12             | 13             | <sup>1</sup> 0  | <sup>1</sup> Ô        |

| 10       | <sup>8</sup> 0 | 91             | <sup>11</sup> 1 | 10                    |

#### **5**. 1p/0p

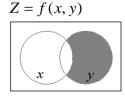

Draw a circuit with **NOR**-gates that corresponds to the Venn-diagram in the figure. (white area = 0, dark area = 1). The complement of the variables are *not* available.

#### **6**. 1p/0p

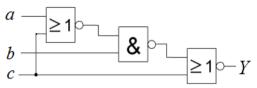

The figure below shows a circuit with two NOR gates and one NAND-gate. Simplify the function Y = f(a, b, c) as much as possible.

#### **7.** 1p/0p

Give an expression for the logical function realized by the CMOS circuit in the figure? Give the function on the SoP form. Y = f(A, B, C) = ?

#### **8**. 1p/0p

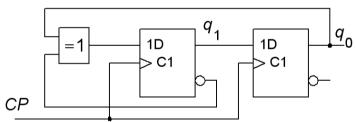

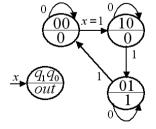

A synchronous counter as shown above starts with the state  $q_1q_0 = 00$ . Specify the **count sequence** for the next four clock pulses.

#### **9.** 1p/0p

For a JK-flip-flop, as you probably remember, the following rules apply:

JK: 00 Q remains the same

*JK*: 01 *Q* is reset to 0

JK: 11 Q toggles value

*JK*: 10 *Q* is set to 1

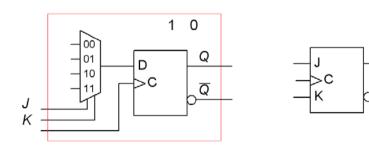

Show (draw) how to make a JK-flip-flop of the D flip-flop and one 4: 1 multiplexer. In addition to Q and its inverse  $\overline{Q}$ , there are constants 1 and 0 available. A copy of the figure is also on the submission sheet.

#### **10.** 1p/0p

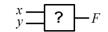

The following is the VHDL code for a logic function. What is the function?

```

library ieee;

use ieee.std_logic_1164.all;

entity GATE_ent is

port( x: in std_logic;

y: in std_logic;

F: out std_logic

);

end GATE_ent;

architecture behv of GATE_ent is

begin

process(x, y)

begin

if (x='0') and y='0') then

F <= '1';

F <= '0';

end if;

end process;

end behv;

```

### Part A2: Methods

*Note! Part A2 will only be corrected if you have passed part A1* ( $\geq 6p$ )

11. 4p Light Gun - emergency equipment for traffic control tower.

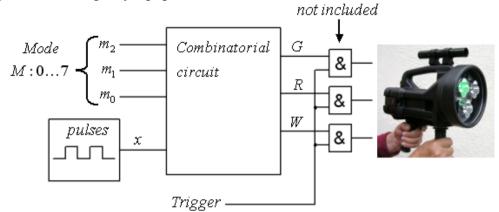

You shall construct a combinatorial circuit for a signal lamp for traffic control tower (emergency).

With an 8-position binary coded switch one selects Mode M:  $m_2m_1m_0$ .

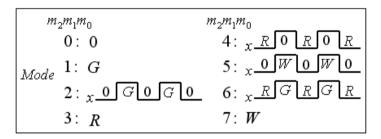

Modes: Turned off, steady green (*G*) light, flashing green light, steady red (*R*) light, flashing red light, flashing white light alternately green and red light, and steady white (*W*) light. Flashing lights are controlled by *x* pulses from a pulse generator.

See the figures. A trigger circuit with three AND gates are also in the figure (for eg. Morse signaling), but this part of the equipment is given, and is not included in the task.

- a) (1p) Set up the **truth table** for the relationship between GRW and  $xm_2m_1m_0$ .

- **b**) (2p) Draw the Karnaugh maps for the three output signals GRW and derive the **minimized** expressions for  $G = f(x, m_2, m_1, m_0)$ ,  $R = f(x, m_2, m_1, m_0)$  and  $W = f(x, m_2, m_1, m_0)$  on SoP-form.

- c) (1p) Draw the **combinatorial circuit** using optional gates. (No inverted variables are available).

#### **12**. 6p

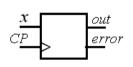

A synchronous sequential circuit, a Moore machine, have one input signal x and one output signal out. The circuit state diagram is shown in the figure below right. In the figure is shown where  $x q_1 q_0$  and out is placed in the state symbol. If the circuit would "end up" in a state outside of the sequence described by the state diagram, the circuit should remain in the state but with out = 0 and an additional output error = 1. The additional output error should always be 0 otherwise.

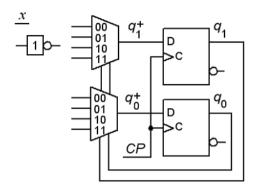

The Moore machine uses D-flip-flops.

- a) (1p) Derive the **encoded state table**.  $q_1^+q_0^+=f(x,q_1q_0)$

- **b**) (2p) Derive minimized expressions for **next state**.

$$q_1^+ = f(x, q_1 q_0)$$

$q_0^+ = f(x, q_1 q_0)$

c) (1p) Derive minimized expressions for the output functions.

$out = f(q_1q_0)$  error =  $f(q_1q_0)$  also draw wiring diagram for these with optional gates.

**d**) (2p) Construct the circuit, use **two 4:1 multiplexers** and not more than one inverter to the next state functions  $q_1^+ = f(x, q_1 q_0)$   $q_0^+ = f(x, q_1 q_0)$

You should indicate what is to be connected to multiplexers data inputs. See the figure to the right.

$$q_1^+: mux_{00} = ?, mux_{01} = ?, mux_{10} = ?, mux_{11} = ?$$

$q_0^+: mux_{00} = ?, mux_{01} = ?, mux_{10} = ?, mux_{11} = ?$

## Part B. Design Problems

*Note! Part B will only be corrected if you have passed part A1+A2* ( $\geq 11p$ ).

13. 5p Synchronous sequential circuit. Detector for specific event.

For a Moore machine applies to the output signal z = 1 if and only if the input signal is w = 1 at the clock pulse, and if of the previous clock pulses at exactly one time the input signal was 1, and at least one time the input signal was 0. Otherwise, the output is 0.

(After a short reset pulse of clr = 1, the machine is ready to detect the "event" again).

a) (3p) Derive the state table and state diagram based on the description in the text.

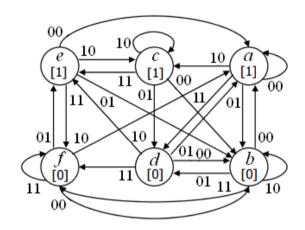

A **completely different Moore machine** has two input signals and one output signal. The machine has six states according to the state diagram in the right figure. Output value is written in square brackets inside the states [].

**b)** (2p) State **minimize** the machine, and derive the **state table** and **state diagram** of the minimized circuit.

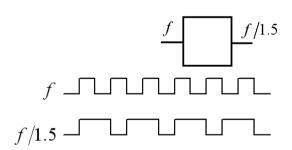

**14.** 5p Frequency divider with ratio 1:1.5.

A computer system have a 90 MHz clock. We want to divide the frequency by a factor of **1.5** down to a frequency of 60 MHz. For this you need an asynchronous sequential circuit. See the figure.

- a) Set up a proper flow table for the sequence circuit. Draw the state diagram.

- **b**) Do a suitable **state assignement** with an exitation table which gives a circuit that is **free of critical race**. (Comment on how this has been achieved).

You should also derive **hazard free expressions** (comment on how this has been achieved) for the next state and an **expression for output**. You do not need draw any schematic.

## Good Luck!

## Submission sheet for Part A1 Sheet 1

(remove and hand in together as sheet no 1 with your answers for part A2 and part B)

| Last name:     | Given name: | Given name: |  |  |

|----------------|-------------|-------------|--|--|

| Personal code: | Sheet:      | 1           |  |  |

| Write down your answers for the questions from Part A1 (1 to 10) |                                                                           |  |  |  |  |

|------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|

| Question                                                         | Answer                                                                    |  |  |  |  |

| 1                                                                | $f(x, y, z) = \{PoS\}_{\min} = ?$                                         |  |  |  |  |

| 2                                                                | $S_0 = ?$ $C_{out0} = ?$                                                  |  |  |  |  |

| 3                                                                | $x \cdot y$ (8 bit 2-complement) = ?                                      |  |  |  |  |

| 4                                                                | $Y = \{SoP\}_{\min}$                                                      |  |  |  |  |

| 5                                                                | $Z = f(x, y)$ $\geq 1$                                                    |  |  |  |  |

| 6                                                                | Y = f(a, b, c)                                                            |  |  |  |  |

| 7                                                                | Y = f(A, B, C) = ?                                                        |  |  |  |  |

| 8                                                                | $q_1q_0 = 00 \rightarrow ?? \rightarrow ?? \rightarrow ?? \rightarrow ??$ |  |  |  |  |

| 9                                                                | 1 0 (VHDL program) What is the function? $x \rightarrow F$                |  |  |  |  |

This table is completed by the examiner!!

| This table is completed by the examiner. |              |    |                    |    |                   |       |  |

|------------------------------------------|--------------|----|--------------------|----|-------------------|-------|--|

| <b>Part A1</b> (10)                      | Part A2 (10) |    | <b>Part B</b> (10) |    | <b>Total</b> (30) |       |  |

| Poäng                                    | 11           | 12 | 13                 | 14 | Sum               | Grade |  |

|                                          |              |    |                    |    |                   |       |  |

|                                          |              |    |                    |    |                   |       |  |