# Written exam for IE1204/5 Digital Design with solutions Thursday 29/10 2015 9.00-13.00

## **General Information**

Examiner: Ingo Sander.

Teacher: William Sandqvist phone 08-7904487

Exam text does not have to be returned when you hand in your writing.

*Aids:* No aids are allowed! The exam consists of three parts with a total of 14 tasks, and a total of 30 points:

**Part A1 (Analysis)** containes ten short questions. Right answer will give you one point. Incorrect answer will give you zero points. The total number of points in Part A1 is 10 points. To pass the **Part A1 requires at least 6p**, *if fewer points we will not look at the rest of your exam*.

Part A2 (Methods) contains two method problems on a total of 10 points.

To **pass the exam** requires at least **11 points** from A1 + A2, *if fewer points we will not look at the rest of your exam*.

Part B (Design problems) contains two design problems of a total of 10 points. Part B is

corrected only if there are at least 11p from the exam A- Part.

**NOTE** ! At the end of the exam text there is a submission sheet for Part A1, which shall be

separated to be submitted together with the solutions for A2 and B.

For a passing grade (E) requires at **least 11 points on the exam**. If exactly 10p from A1(6p)+A2(4p), (FX), completion to (E) will be offered.

Grades are given as follows:

| 0 - | 11 – | 16 – | 19 – | 22 – | 25 |  |

|-----|------|------|------|------|----|--|

| F   | E    | D    | С    | В    | А  |  |

The result is expected to be announced before Thursday 19/11 2015.

## Part A1: Analysis

Only answers are needed in Part A1. Write the answers on the submission sheet for Part A1, which can be found at the end of the exam text.

**1.** 1p/0p

A function f(x, y, z) is described by the expression:  $f(x, y, z) = \overline{x \cdot y \cdot z} + x \cdot \overline{y \cdot z} + \overline{(y + z)}$ Write down the function maxterms, eg. the function as a product of sums.  $f(x, y, z) = \{PoS\} = ?$  **1.** Proposed solution  $f(x, y, z) = \overline{x \cdot y \cdot z} + x \cdot \overline{y \cdot z} + \overline{(y + z)} = (\overline{x + y + z}) + x\overline{yz} + \overline{yz} = \overline{x + y + z} + \overline{yz}(x + 1) =$

$=\overline{x}+\overline{z}+\overline{y}(1+\overline{z})=(\overline{x}+\overline{y}+\overline{z})$  only one maxterm is needed

#### **2.** 1p/0p

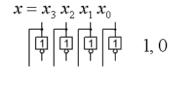

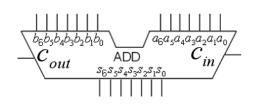

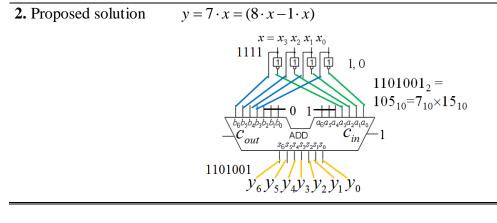

A four bit unsigned integer  $x (x_3x_2x_1x_0)$  is to be multiplicated by the constant **7**. This is done by connecting the number x to a seven bit adder that is configured to do the operation  $y = 7 \cdot x = (8 \cdot x - 1 \cdot x)$

Draw how the adder is to be configured. Except the four bits in x there are also bits with the values 0 and 1 if needed. You will find a copy of the figure on the submission sheet.

$$\mathcal{Y}_6 \mathcal{Y}_5 \mathcal{Y}_4 \mathcal{Y}_3 \mathcal{Y}_2 \mathcal{Y}_1 \mathcal{Y}_0$$

**3.** 1p/0p

Two binary 6 bit two complement numbers are added. What will the result be expressed as a signed decimal number?

001011

+ 101110

$\boxed{\begin{array}{c} \hline \\ = \text{ signed decimal } \pm ??_{10} \\ \hline \textbf{3. Proposed solution} \\ \hline \begin{array}{c} 001011 + 101110 = 111001 \\ 001011 \\ \hline \begin{array}{c} -2^5 + 11001_2 = -32 + 25 = -7 \\ \hline \begin{array}{c} 001011 + 101110 \\ \hline \begin{array}{c} +101110 \\ \hline 111001 \\ \end{array} \\ \hline \end{array} \\ \hline \end{array} \\ \hline \end{array}$

**4**. 1p/0p

Given is a Karnaugh map for a function of four variables  $y = f(x_3, x_2, x_1, x_0)$ . Write the function as a minimized  $y_{min}$  sum of products, **SoP** form. "-" in the map means "don't care".

| y y            |                |                |                       |                |  |  |

|----------------|----------------|----------------|-----------------------|----------------|--|--|

| $X_3^{1}$      |                | 01             | 11                    | 10             |  |  |

| ×3<br>×20<br>0 | 0_             | <sup>1</sup> 0 | <sup>3</sup> 0        | <sup>2</sup> 1 |  |  |

| 0<br>1         | <sup>4</sup> 1 | 5_             | <sup>7</sup> 1        | <sup>6</sup> 0 |  |  |

| 1<br>1         | 12             | 13             | <sup>1</sup> <b>D</b> | 1 <b>Ó</b>     |  |  |

| 1<br>0         | 81             | <sup>9</sup> 0 | 1 <b>0</b>            | 1 <u>0</u>     |  |  |

4. Proposed solution  $y = \overline{x_2} \overline{x_0} + x_2 \overline{x_1} + \overline{x_3} x_2 x_0$   $y = \overline{x_2} \overline{x_0} + x_2 \overline{x_1} + \overline{x_3} x_2 x_0$   $x_3 \overline{y} = 0 - 1 0 \overline{30} \overline{21}$  $y = \overline{x_1} \overline{x_1} + \overline{x_2} \overline{x_1} + \overline{x_3} \overline{x_2} x_0$

#### **5**. 1p/0p

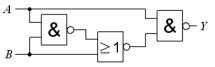

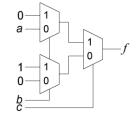

The figure bellow shows a circuit with two NAND gates and one NOR-gate. Simplify the function Y = f(A, B) as much as possible.

**5.** Proposed solution

$$\underline{Y} = A \cdot \overline{A \cdot B} + B = \overline{A} + \overline{A \cdot B} + B = \overline{A} + \overline{A} + \overline{B} + B = 1$$

#### **6.** 1p/0p

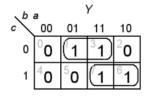

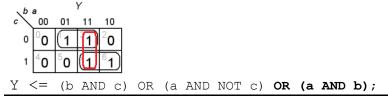

A logic function of three variables c b a is realized with multiplexors. Write the function on minimized **PoS** form (as a product of sums).

# $f(c,b,a) = \{PoS\}_{\min} = ?$

6. Proposed solution  $f(c,b,a) = \{SoP\} = 0 \cdot bc + a \cdot \bar{b}c + 1 \cdot b\bar{c} + 0 \cdot \bar{b}c = a\bar{b}c + b\bar{c} = a\bar{b}c + (a + \bar{a})b\bar{c} = a\bar{b}c + ab\bar{c} + \bar{a}b\bar{c}$   $\overset{bc}{\xrightarrow{0}} \overset{00}{\xrightarrow{0}} \overset{01}{\xrightarrow{1}} \overset{11}{\xrightarrow{1}} \overset{10}{\xrightarrow{1}} f(c,b,a) = \{PoS\}_{\min} = (\bar{b}+\bar{c})(b+c)(a+\bar{c}) \quad or \quad = (\bar{b}+\bar{c})(b+c)(a+b)$

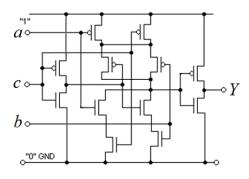

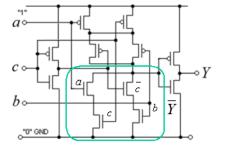

#### 7. 1p/0p Give an expression for the logical function realized by the CMOS circuit in the figure? Y = f(a,b,c) = ?

#### 7. Proposed solution

$PDN: \quad \overline{Y} = ac + b\overline{c}$  $\Rightarrow \overline{\overline{Y}} = Y = ac + b\overline{c}$

**CMOS** Multiplexor

#### **8**. 1p/0p

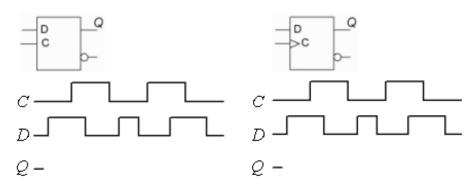

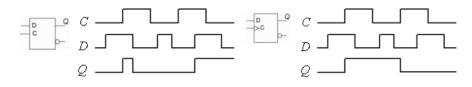

Complete the timing diagram for the D-latch and D-flipflop by drawing signal Q for booth cases. Draw the figure so that it is clear **what** is causing the changes in the Q!

#### 8. Proposed solution

**9.** 1p/0p

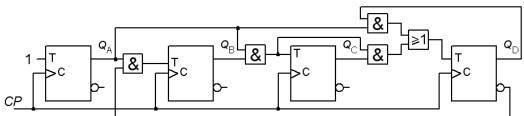

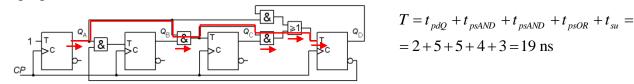

The figure shows a synchronous decade counter ( $Q_DQ_CQ_BQ_A \quad 0...9$ ). Mark (= draw in the figure on the answer sheet) the **critical path** that determines how fast the counter can count. Calculate the minimum time *T* [ns] between the clock pulses that still provides safe operation.

Gates:  $t_{pdOR} = 4$ ,  $t_{pdAND} = 5$  [ns] Flip-flops:  $t_{su} = 3$ ,  $t_h = 1$ ,  $t_{pdQ} = 2$  [ns]

9. proposed solution

#### **10.** 1p/0p

Below is the VHDL code for a 2: 1 multiplexer. The multiplexer Karnaugh map is shown at right. Complete code so that it becomes a **Hazard free** MUX. The line of code is also available on the answer sheet.

```

-- import std logic from the IEEE library

library IEEE;

use IEEE.std_logic_1164.all;

-- this is the entity

entity MUX is

port (

a : in std logic;

b : in std logic;

: in std logic;

С

Y

: out std logic);

end entity MUX;

-- this is the architecture

architecture gates of MUX is

begin

Y <= (b AND c) OR (a AND NOT c)

end architecture gates;

```

#### 10. Proposed solution

## Part A2: Methods

*Note!* Part A2 will only be corrected if you have passed part A1 ( $\geq 6p$ )

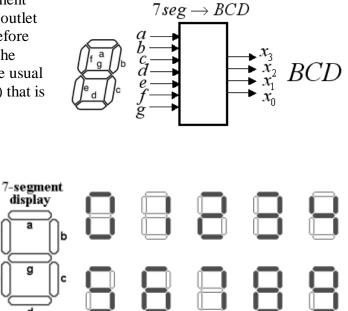

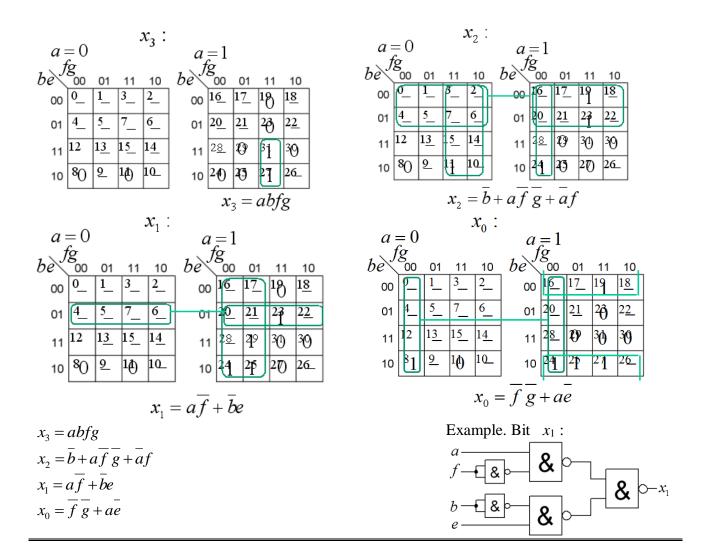

**11.** 5p One older instrument has a seven segment display with seven light bulbs, but it lacks an outlet for connection to a computer. One could therefore need a combinatorial circuit that connects to the bulbs and then converts 7-segment code to the usual BCD code (normal binary coded digits 0 to 9) that is used by a variety of other equipments.

**a)** (1p) Set up the **truth table** for the ten BCD numbers. Black segment is "1" in figure.  $(x_3x_2x_1x_0)_{BCD} = f(abcdefg)$

**b**) (1p) Inspect the **truth table**. You can discover that even if up to two of the segments are excluded as inputs, the relationship remains distinct between image segments and BCD digits. Find one/two segments that you can do without? Derive the **new truth-table** without this/these segments.

c) (2p) Draw the karnaugh maps for the four BCD-code bits and derive the **minimized expressions** for  $x_3 x_2 x_1 x_0$  in SoP-form. Segment combinations that never occurs should be exploited as don't care. (With the excluded segments in the truth table, the number of variables will be manageable).

d) (1p) Choose yourself one of the expressions  $x_3 x_2 x_1 x_0$  and realize it using only 2 input NAND gates. (No inverted variables are available)

| <b>11.</b> P | roposed solu | ition |                   |                                                                                                  |                   |

|--------------|--------------|-------|-------------------|--------------------------------------------------------------------------------------------------|-------------------|

|              | abcdefg      |       | $x_3 x_2 x_1 x_0$ | 7-segment<br>display abefg                                                                       | $x_3 x_2 x_1 x_0$ |

| 126          | 1111110      | 0     | 0000              |                                                                                                  | 0000              |

| 48           | 0110000      | 1     | 0001              |                                                                                                  | 0001              |

| 109          | 1101101      | 2     | 0010              |                                                                                                  | 0010              |

| 121          | 1111001      | 3     | 0011              | Segment <i>a</i> is necessary distinguish<br>between "1" and "7". Segment <i>e</i> is 25 11001 3 | 0011              |

| 51           | 0110011      | 4     | 0100              | needed to distinguish between "8" 11 01011 4                                                     | 0100              |

| 91           | 1011011      | 5     | 0101              | from "9" and "5" from "6". 19 10011 5                                                            | 0101              |

| 95           | 1011111      | 6     | 0110              | Segments c and d could be 23 10111 6                                                             | 0110              |

| 112          | 1110000      | 7     | 0111              | excluded without the encoding<br>becoming ambiguous. See the 24 11000 7                          | 0111              |

| 127          | 1111111      | 8     | 1000              | figure. This can be used to 31 11111 8                                                           | 1000              |

| 123          | 1111011      | 9     | 1001              | simplify the problem down to 5 27 11011 9 variables.                                             | 1001              |

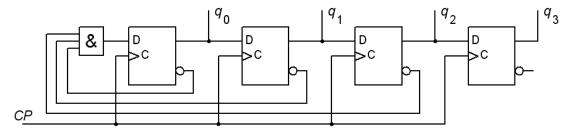

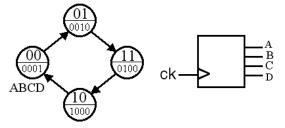

10. 5p The figure shows a "self-correcting ring counter" counting the "one hot" sequence  $q_3q_2q_1q_0$  0001, 0010, 0100, 1000.

**a**) (2p) Analyze the sequential circuits in the figure and draw the **full state diagram** and the **full state table**. If the counter would start in any other state than any of the four desired "one hot" states, how many clock pulses are required, in the worst case, before the counter has "corrected" this and ends up in the correct sequence?

**b**) (3p) You can also get the same "one-hot" sequence from a Moore machine with four states, see the state diagram to the right. Derive this sequential circuit with D-flip-flops and optional gates. Use the state encoding from the state diagram. Draw the schematic of the circuit.

## Part B. Design Problems

*Note!* Part B will only be corrected if you have passed part  $A1+A2 (\geq 11p)$ .

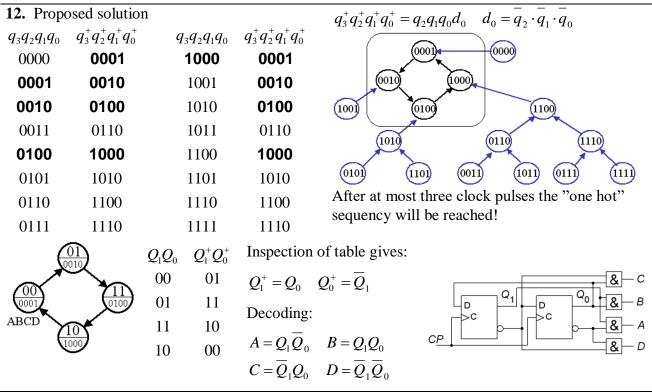

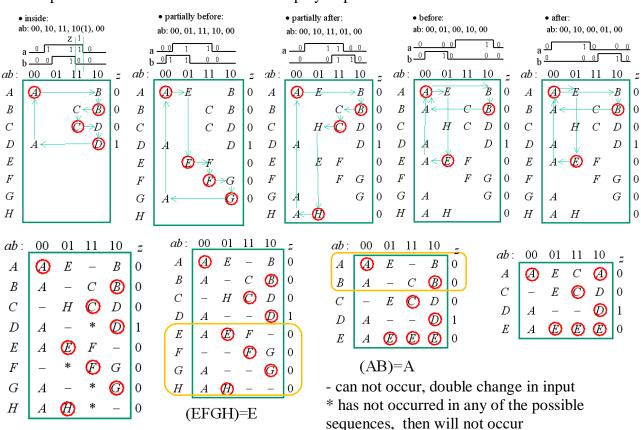

13. 4p Sequence Detector. Different inputs three in a row.

You will design a synchronous sequential circuit, in the form of a positive edge-triggered Moore machine with D flip-flops. The input signals a and b are synchronized with the clock pulses C. The output signal z will be 1 when a and b are different in at least three consecutive clock pulse intervals. For other sequences z must be equal to 0.

a) (2p) Derive the circuit state table and draw the state diagram.

b) (1p) Use the Gray code to encode the states and derive the **encoded state table**. Derive the minimized expressions for **next state** and for the **output**.

c) (1p) Draw the **next state decoder circuit**, there is only access to AND, OR, and XOR gates.

**13.** Proposed solution

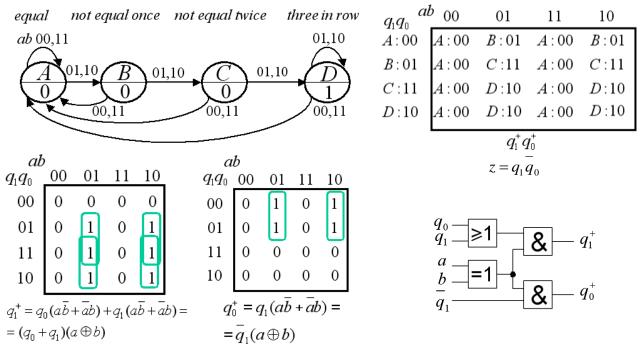

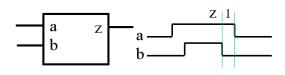

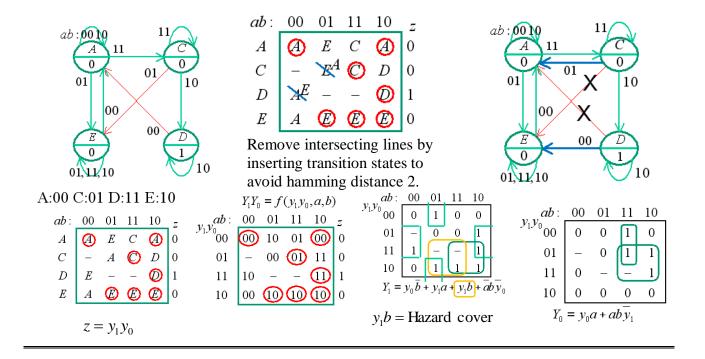

#### 14. 6p Inside pulse detector.

An asynchronous sequential circuit "Compares" pulses received on two inputs **a** and **b**. The pulse at the **b** input is always a little shorter than the pulse of **a**, and there will be at most one **b**-pulse during the interval **a**. **b**-pulses will arrive randomly relative to the **a**-pulse. (There are no **exact** simultaneous events).

Sequence circuit must indicate the case when **b** is started (becomes one) after a has started (become one), and **b** has finished (become 0) before **a** finish (become 0). The output **z** will then be = 1 from **b**'s trailing edge to **a**'s trailing edge. **z** must be 0 for all other cases. See the figure time diagram illustrating this case.

**a**) First, set up a proper **flow table** for the sequence circuit. You don't need from the beginning to care about minimizing the number of states. All positions in the table that can not occur should be treated as don't care.

**b**) **Simplify the state diagram** by combining compatible state. (Hint. Various solutions are possible, there is among them a solution with four states).

c) Do a suitable **state assignement** with an exitation table which gives a circuit that is **free of critical race**. (Hint. Various solutions are possible, there is a solution with two state variables exploiting unstable transition states and uncritical race).

You should also derive **hazard free expressions** for the next state and an **expression for output**, and draw the **circuits** with the use of optional gates.

#### 13. Proposed solution – derive state chart step by step

Good Luck!

## Submission sheet for Part A1 Sheet 1

(remove and hand in together with your answers for part A2 and part B)

Last name:

Given name:

Personal code: Sheet:

1

٦

Write down your answers for the questions from Part A1 (1 to 10) Ouestion A ----

| Question | Answer                                                                                              |      |                                         |

|----------|-----------------------------------------------------------------------------------------------------|------|-----------------------------------------|

| 1        | $f(x, y, z) = \{PoS\} = ?$                                                                          |      |                                         |

| 2        | $y = 7 \cdot x = (8 \cdot x - 1 \cdot x)$                                                           | 3    | Signed decimal $\pm$ ?? <sub>10</sub> = |

|          |                                                                                                     |      |                                         |

|          | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                              |      |                                         |

|          | $\mathcal{Y}_6 \mathcal{Y}_5 \mathcal{Y}_4 \mathcal{Y}_3 \mathcal{Y}_2 \mathcal{Y}_1 \mathcal{Y}_0$ |      |                                         |

| 4        | $f(x_3, x_2, x_1, x_0) = \{SoP\}_{\min} = ?$                                                        | 5    | Y = f(A, B) = ?                         |

| 6        | $f(c,b,a) = \{PoS\}_{\min} = ?$                                                                     | 7    | Y = f(a,b,c) = ?                        |

| 8        |                                                                                                     |      |                                         |

| 9        |                                                                                                     | ┝┰ᡒᡀ | T [ns] =                                |

| 10       | Y <= (b AND c) OR (a AND NOT                                                                        | C)   |                                         |

#### This table is completed by the examiner!!

| <b>Part A1</b> (10) | Part A2 (10) |    | <b>Part B</b> (10) |    | <b>Total</b> (30) |       |

|---------------------|--------------|----|--------------------|----|-------------------|-------|

| Poäng               | 11           | 12 | 13                 | 14 | Sum               | Grade |

|                     |              |    |                    |    |                   |       |

|                     |              |    |                    |    |                   |       |