# Written reexam IE1204/5 Digital Design Friday 13/4 2017 14.00-18.00

#### General Information

Examiner: Ingo Sander.

*Teacher*: Kista, William Sandqvist tel 08-7904487 *Teacher*: Valhallavägen, Ahmed Hemani 08-7904469

Exam text does not have to be returned when you hand in your writing.

Aids: No aids are allowed!

The exam consists of three parts with a total of 14 tasks, and a total of 30 points:

**Part A1** (**Analysis**) containes ten short questions. Right answer will give you one point. Incorrect answer will give you zero points. The total number of points in Part A1 is 10 points. To pass the **Part A1** requires at least 6p, if fewer points we will not look at the rest of your exam.

Part A2 (Methods) contains two method problems on a total of 10 points.

To **pass the exam** requires at least **11 points** from A1 + A2, if fewer points we will not look at the rest of your exam.

**Part B** (**Design problems**) contains two design problems of a total of 10 points. Part B is corrected only if there are at **least 11p** from the exam A- Part.

**NOTE!** At the end of the exam text there is a submission sheet for Part A1, which shall be separated and be submitted together with the solutions for A2 and B.

For a passing grade (**E**) requires at **least 11 points on the exam**. If exactly 10p from A1(6p)+A2(4p), (FX), completion to (E) will be offered.

**Grades** are given as follows:

| 0 – | 11 – | 16 – | 19 – | 22 – | 25 |

|-----|------|------|------|------|----|

| F   | Е    | D    | C    | В    | A  |

The result is expected to be announced before Friday 5/5 2017.

# Part A1: Analysis

Only answers are needed in Part A1. Write the answers on the submission sheet for Part A1, which can be found at the end of the exam text.

#### **1.** 1p/0p

A function f(x, y, z, w) is described as:

$$f(x, y, z, w) = y(\overline{z \oplus w}) + \overline{z}w + x\overline{z}w + x\overline{z}w + x\overline{z}w + x\overline{z}w$$

Write down the function as a minimized sum of products.

$$f(x, y, z, w) = \{SoP\}_{\min} = ?$$

#### **2.** 1p/0p

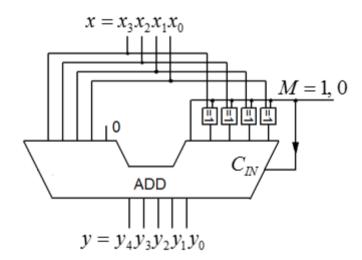

A 5-bit adder is connected to **multiply** a binary unsigned 4-bit number  $x = x_3x_2x_1x_0$  with a **constant** k,  $y = k \cdot x$ .

A mode signal M (with 4 XOR-gates) changes between two values of the constant,  $M = 0 \rightarrow k_0$  or  $M = 1 \rightarrow k_1$ . What values has the constants  $k_0$  and  $k_1$ ?

(Hint! Test with some number x to see what the corresponding product y will be for M = 1 and M = 0).

#### **3.** 1p/0p

Two two's complement 16-bit number are (hexadecimal)  $x_{16} = \text{FFFC}$  and  $y_{16} = 0004$ . What will the sum s = x + y of the two numbers be? Express this number s as a decimal number with sign  $\pm s_{10} = ?$

#### **4**. 1p/0p

Given is a Karnaugh map for a function of four variables  $Y = f(x_3, x_2, x_1, x_0)$ . Write the function  $Y_{\min}$ , as a minimized sum of products, on **SoP** form. "-" in the map means "don't care".

| $x_3x_2$ | х<br>00        | 01                    | 11             | 10             |

|----------|----------------|-----------------------|----------------|----------------|

| 00       | 0              | <sup>1</sup> <b>1</b> | <sup>3</sup> 0 | 2 <b>_</b>     |

| 01       | 4 _            | 5_                    | <sup>7</sup> 0 | <sup>6</sup> 1 |

| 11       | <sup>1</sup> 0 | 13                    | 16             | 10             |

| 10       | <sup>8</sup> 1 | о<br>О                | 10             | 10             |

#### **5**. 1p/0p

We need a three-input OR-gate to the three variables a b c. We only have two-input NAND-gates (max 6). How should these be used and connected? We also have the inverted versions of the variables  $\bar{a} \bar{b} \bar{c}$  if this could help. Draw the schematic with the gates on the submission sheet.

$$\begin{array}{c}

a \\

b \\

c

\end{array} = \underbrace{\phantom{a}}_{c} = \underbrace{\phantom{a}}_$$

#### **6.** 1p/0p

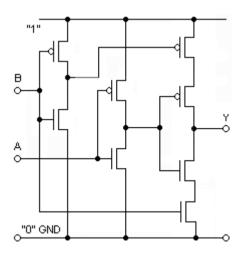

Three-state logic. What is needed to do with the inputs *A* or *B* to put the gate output *Y* in the high impedance three-state?

#### **7**. 1p/0p

The state table in the figure is about a synchronous Mealy-automata.Draw the complete state diagram. Answer on the submission sheet.

| State | Next State |       | Out   | Z     |

|-------|------------|-------|-------|-------|

|       | w = 0      | w = 1 | w = 0 | w = 1 |

| A     | A          | В     | 0     | 0     |

| В     | A          | В     | 0     | 1     |

#### **8**. 1p/0p

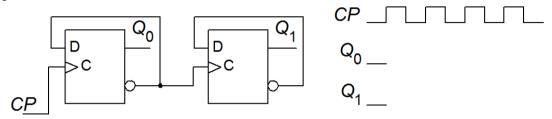

An asynchronous counter in the figure above starts in the state  $q_1q_0 = 00$ . Complete the timing diagram. Answer on the submission sheet.

#### **9.** 1p/0p

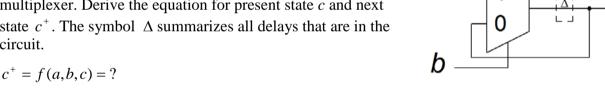

The figure shows a kind of asynchronous latch made with a multiplexer. Derive the equation for present state c and next state  $c^+$ . The symbol  $\Delta$  summarizes all delays that are in the circuit.

#### **10.** 1p/0p

The VHDL code below describes a kind of synchronous counter. Suppose that the counter starts on count = 0. What will the count value be after 12 clock pulses?

```

bcd:

PROCESS(clk)

BEGIN

IF rising_edge(clk) THEN

IF (count = 5) THEN

count <= 0;

count <= count+1;</pre>

END IF;

END IF;

END PROCESS;

```

#### Part A2: Methods

*Note! Part A2 will only be corrected if you have passed part A1* ( $\geq 6p$ )

#### **11.** 5p

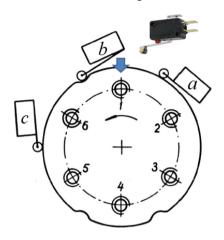

A machine tool has an index table with six positions 1, 2, 3, 4, 5, 6 distributed along the perimeter with  $60^{\circ}$  of division angle. The table position is detected with three switches a b c against three recesses along the table's perimeter. When a switch is in a recess, the signal is '0', and otherwise '1'. An example: when the index table is in position 1 (at the arrow in the figure) then a and c becomes '1' (at the perimeter) and b becomes '0' (inside a recess).

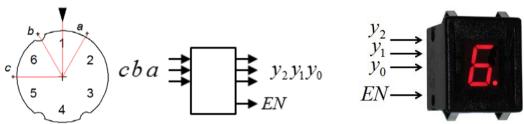

One wants to indicate the table position with a numeric display that has inputs for binary code  $y_2y_1y_0$ . The display also has an enable input *EN*. To show the numbers it is required that EN = '1', the display is off when EN = '0'.

- a) (2p) Derive the truth table for the relationship between position and binary switches  $y_2y_1y_0 = f(c,b,a)$ .

- b) (1p) When the table is switching between positions the display should be kept off (EN = 0). Construct a combinatorial network (gate) for this function EN = f(c,b,a).

- c) (2p) Construct the network  $y_2y_1y_0 = f(c,b,a)$  minimize with the help of Karnaugh map and exploite don't care. Use NAND-gates. Draw the schematic.

#### **12**. 5p

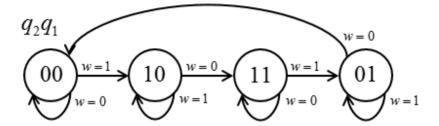

Construct a synchronous sequential circuit, with an input w, that follows the state diagram below.

a) (1p) Set up the encoded state table.

$$q_2^+ q_1^+ = f(w q_2 q_1)$$

(1p) Derive minimized expressons for next state

$$q_2^+ = ? \quad q_1^+ = ?$$

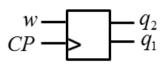

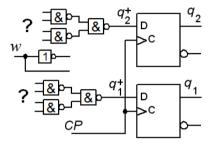

- (1p) Realize the sequence network with D flip-flops and NAND gates according to the figure. Draw your solution.

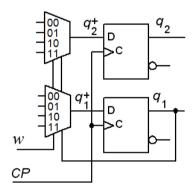

- b) (2p) Realize the sequence network with D flip-flops and 4: 1 Multiplexers according to the figure. The answer must be motivated.

$$q_{2}^{+}: mux_{00} = ?, \quad mux_{01} = ? \quad mux_{10} = ?, \quad mux_{11} = ?$$

$q_{1}^{+}: mux_{00} = ?, \quad mux_{01} = ? \quad mux_{10} = ?, \quad mux_{11} = ?$

### Part B. Design Problems

*Note! Part B will only be corrected if you have passed part A1+A2* ( $\geq$ 11p).

**13.** 5p Synchronous sequential circuit. Detector for specific event.

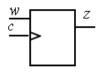

Detect when the particular sequence of ... 1010 ... occurs in a sequence of bits to input w. The signal w is synchronized with the clock pulses c. Each time the correct bit sequence appears then z=1.

The sequence detector output z should be '1' in the clock interval directly after the sequence has occurred (Moore automata). At start is w = 0. See the figure.

The sequence circuit should be a Moore-automata constructed with positive edge triggered D flip-flops.

- a) (2p) Draw the **State Diagram** and set up the **State Table**.

- **b**) (2p) Set up the **Encoded State Table**, and use *binary code* as the state code. Derive minimized expressions for **Next State decoder** and **Output decoder**.

- c) (1p) Draw Schematic, use any optional gates.

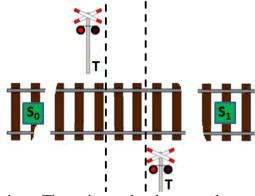

- **14.** 5p Warning signal for a railway crossing.

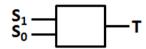

A road crosses a railway without barriers. At the intersection are traffic lights T that warn when a train is nearby. Two sensors  $S_0$  and  $S_1$  detects when trains pass over them (S = '1').

Construct an asynchronous sequential circuits that keep the traffic lights on (T = '1') as long as there is a part of a train on the route between  $S_0$  and  $S_1$ .

Trains can come from both directions. The train can be shorter or longer than the distance  $S_0$ - $S_1$ . Only one train at a time is passing between  $S_0$  and  $S_1$ .

- a) (2p) Draw the state diagram.and set up a proper flow table for the sequential circuit.

- **b)** (2p) Make a suitable **state assignment** with an **exitation table** that provides circuits that are free from critical race (comment on how you achieved this). You will also develop the hazard free **expressions** for the **next state** (comment on how you achieved this) as well as an expression for **output**.

- c) (1p) Draw the circuit diagram. (Use optional gates).

## Good Luck!

# Submission sheet for Part A1 Sheet 1

( remove and hand in together with your answers for part A2 and part B )

| Last name:     | Given name: |   |

|----------------|-------------|---|

| Personal code: | Sheet:      | 1 |

| Write    | down your answers for the questions from Part A1 ( 1 to 10 )                                                                               |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Question | Answer                                                                                                                                     |

| 1        | $f(x, y, z, w) = \{SoP\}_{\min} = ?$                                                                                                       |

| 2        | $M = 0$ $k_0 = ?$ $M = 1$ $k_1 = ?$                                                                                                        |

| 3        | $FFFC+0004 = \pm s_{10} = ?$                                                                                                               |

| 4        | $Y = \{SoP\}_{\min}$                                                                                                                       |

| 5        | $ \begin{array}{c} a \\ b \\ c \end{array} = 21 - Y $ $ \begin{array}{c} a \\ b \\ c \end{array} = 24 - 24 - 24 - 24 - 24 - 24 - 24 - 24 $ |

| 6        | $B, A ? \rightarrow Y = \text{three-state}$                                                                                                |

| 7        | $ \begin{array}{c} w = 0 \\ z = 0 \end{array} $                                                                                            |

| 8        | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                      |

| 9        | $c^+ = f(a,b,c) = ?$                                                                                                                       |

| 10       | After 12 clock pulses the count is:                                                                                                        |

This table is completed by the examiner!!

| <b>Part A1</b> (10) | Part A2 (10) |    | <b>Part B</b> (10) |    | <b>Total</b> (30) |       |

|---------------------|--------------|----|--------------------|----|-------------------|-------|

| Points              | 11           | 12 | 13                 | 14 | Sum               | Grade |

|                     |              |    |                    |    |                   |       |

|                     |              |    |                    |    |                   |       |