This course treats the most important component in all integrated circuits - the MOSFET-transistor that is produced in silicon with nanometer dimensions. The focus is on low power CMOS-technology.

Course main content

- Basic physics for the MOS-system and formulation of approximate current-voltage relations for the MOS-transistor. Compact physics based models for circuit simulation. Modelling of process corners.

- Scaling theory and technology nodes for CMOS technology.

- Modern CMOS device topologies, SOI and FinFET, 3D-structures including nanowire/sheet.

- Power consumption, crosstalk and scaling of interconnects.

- Memory technologies, charge based, resistive or based on other physical principles.

- New technologies and applications as for instance spintronics, 2D-materials, and 3D-fabrication.

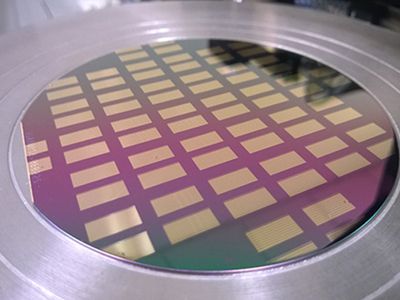

- Circuit design for nanometer CMOS, ASIC, FPGA, design rules, robustness, testing, reliability, error analysis, variability on component, chip and wafer level.