- ASIC konstruktionsflöde

- ASIC teknologier

- Klassifikation och specifikation av målkrav för logisk syntes

- Statisk tidsanalys

- Syntes av tillståndsmaskiner

- Test och verifikation

- Konstruktion för låg effekt och logisk syntes

- Konstruktion för testbarhet

- Teknologimappning

- Fysisk konstruktion

IL2200 ASIC-design metodik med hårdvarubeskrivande språk 7,5 hp

Denna kurs är avvecklad.

Avvecklingsbeslut:

Ingen information tillagd

Information per kursomgång

Kursomgångar saknas för aktuella eller kommande terminer.

Kursplan som PDF

Notera: all information från kursplanen visas i tillgängligt format på denna sida.

Kursplan IL2200 (HT 2008–)Innehåll och lärandemål

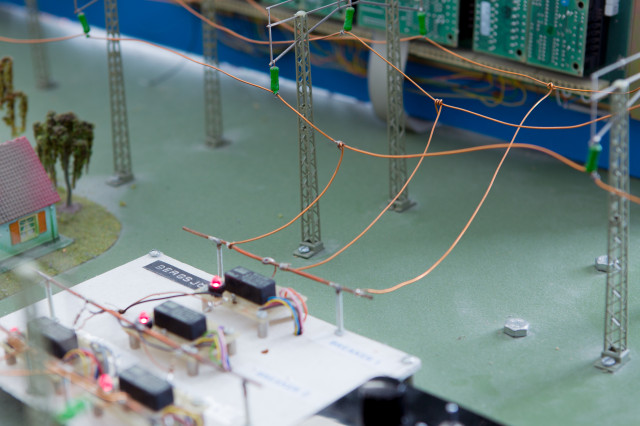

Kursinnehåll

Lärandemål

Efter avslutad kurs ska studenten kunna

- beskriva de olika faserna i konstruktionsflödet för digitala ASIC:ar

- förklara hur icke-funktionella konstruktionskrav påverkar konstruktionsprocessen

- kategorisera olika ASIC-typer och förklara dess teknologi

- förklara hur olika språkkonstruktioner i ett hårdvarubeskrivande språk (HDL) kan realiseras i en ASIC

- introducera extra hårdvara för att förbättra testbarheten i en konstruktion

- benämna och förklara tekniker för test och verifikation av en konstruktion

- styra konstruktionsprocessen genom att ange målkrav och målegenskaper för att få en effektiv ASIC-implementation

- beskriva en konstruktion med en HDL so att den kan implementeras kostnadseffektiv på en ASIC

- använda tekniker för att analysera tidsbeteendet av konstruktionen

Kurslitteratur och förberedelser

Särskild behörighet

IL2217 eller motsvarande.

Kurslitteratur

Kursboken meddelas en månad innan kursstart på kurswebsidan.

Examination och slutförande

Betygsskala

Examination

- TEN1 - Tentamen, 4,5 hp, betygsskala: A, B, C, D, E, FX, F

- LAB1 - Laborationskurs, 3,0 hp, betygsskala: P, F

Examinator beslutar, baserat på rekommendation från KTH:s handläggare av stöd till studenter med funktionsnedsättning, om eventuell anpassad examination för studenter med dokumenterad, varaktig funktionsnedsättning.

Examinator får medge annan examinationsform vid omexamination av enstaka studenter.

När kurs inte längre ges har student möjlighet att examineras under ytterligare två läsår.

Betygsskala: A/B/C/D/E/Fx/F

Övriga krav för slutbetyg

Skriftlig tentamen, 4.5 hp (TEN1: Betyg A-F)

Laborationskurs, 3.0 hp (LAB1: Betyg P,F)

Slutbetyget ges av betyget i den skriftliga tentamen (TEN1).

Laborationskursen måste avslutas under pågående läsår. Annars måste alla laborationer göras om.

Examinator

Etiskt förhållningssätt

- Vid grupparbete har alla i gruppen ansvar för gruppens arbete.

- Vid examination ska varje student ärligt redovisa hjälp som erhållits och källor som använts.

- Vid muntlig examination ska varje student kunna redogöra för hela uppgiften och hela lösningen.

Ytterligare information

Kursrum i Canvas

Ges av

Huvudområde

Utbildningsnivå

Övrig information

ASIC = Application Specific Integrated Circuit

FPGA = Field Programmable Gate Array

VHDL = VHSIC Hardware Description Language

VHSIC = Very High Speed Integrated Circuit