Denna kurs fokuserar pådimensionering påsystemnivåoch trade-off aspekter av system-on-chip (FPGA eller ASIC) konstruktion. Studenterna studerar system egenskaperna hos de viktigaste SoC-komponenter, som beräkningar, minne och interconnect. Studenten lär sig hur komponenterna sätts ihop till ett komplett system med alla viktiga avvägningar, som måste beaktas.

1. Komponenter påsystemnivå

A. Beräkning

i. Software - superskalär, VLIW, ASIPs, Multi-core - homogena, heterogena

ii. Hårdvara - ASIC, FPGA: er och den framväxande CGRAs

b. förvaring

i. SRAM, DRAM, Flash och ny teknik minne

ii. Registrera filer vs SRAM

iii. Centraliserad vs Distribuerad

iv. Påmarker kontra off-chip. cache

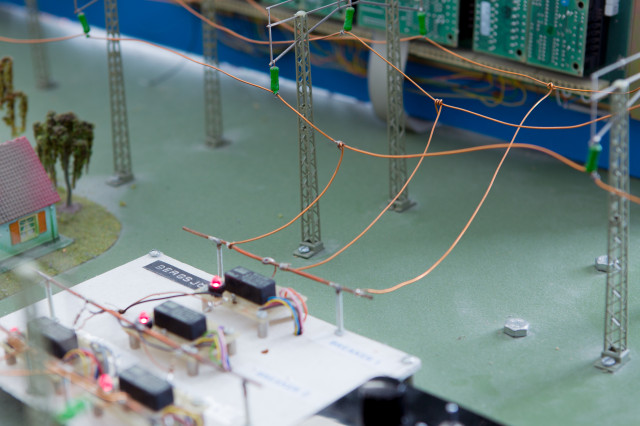

C. Interconnect

i. Interconnect hierarki och lager

ii. Buss typer och topologier

iii. NOC

D. System Level Power Management

i. klocka Domäner

ii. Effekt Domäner

iii. DVFS

iv. Viloläge och Power slussning

2. Avvägningar för systemkonstruktion

A. Kraft, energi, Prestanda och samarbetsområdet.

b. De tre VLSI väggar - frekvens, minne och makt

C. Produktivitet,återanvändbarhet

3. Timing och Synkroniserings frågor

4. VLSI Physical Design

5. ATPG, DFT - Scan och BIST