This course focuses on system level dimensioning and trade-offs aspects of Systems-on-Chip (FPGA or ASIC) design. The students study the system properties of the main SoC components, which are computation, memory and interconnect. The student learns how the components are put together into a complete system with all the important trade-offs, that have to be considered.

1. System Level Components

a. Computation

i. Software–Superscalar, VLIW, ASIPs, Multi-core–homogeneous, heterogeneous

ii. Hardware–ASIC, FPGAs and the emerging CGRAs

b. Storage

i. SRAM, DRAM, Flash and emerging memory technologies

ii. Register Files vs. SRAMs

iii. Centralized vs. Distributed

iv. On chip vs. off chip. Cache

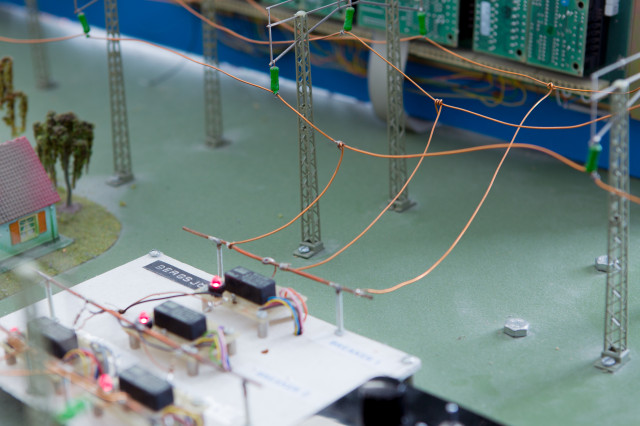

c. Interconnect

i. Interconnect hierarchy and layers

ii. Bus types and topologies

iii. NOC

d. System Level Power Management

i. Clock Domains

ii. Power Domains

iii. DVFS

iv. Hibernation and Power gating

2. System Level Design Trade-offs

a. Power, Energy, Performance and Area.

b. The three VLSI walls–frequency, memory and power

c. Productivity, Reusability

3. Clocking and Synchronisation Issues

4. VLSI Physical Design

5. ATPG, DFT – Scan and BIST