Thesis projects

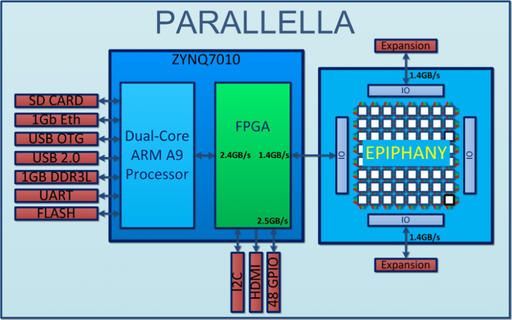

The picture above shows the block diagram of the Parallella board from Adapteva (www.parallella.org, www.adapteva.com). It represents the current trend in computing hardware which leads to multiple and heterogenous cores. Below we outline some degree project proposals that all relate to multi-/manycore architectures and/or heterogenous architectures. They are

suitable for two students each and several of them are also suitable for Bachelor’s level with some adaptation.

Most projects are carried out in within the scope of the Multicore Center at SICS. All thesis projects carried out here have the potential of generating research publications and is therefore an excellent start if you ever want to pursue a research career in the future.

Contact Mats Brorsson, for more information if no other contact person is mentioned in the text below.

Thesis suggestions

Your favorite parallel project here

If you have your own idea for a project, let us know and we can probably make it into a degree project.

Converting PaPP application use-cases to task-based form.

In a large European project, PaPP www.papp-project.eu, there are a number of use-cases being developed. These need to be parallelized using a specific task-centric parallel programming model. This project would involve the parallelization of a selection of these use-cases and with evaluations on at least two different hardware platforms.

Extending the MIR runtime system to the Parallella platform. In other words, building a task-based runtime system for the Parallella.

Parallella is a power-efficient heterogeneous parallel computer with a 16-core Epiphany processor and ARM A9-based host controller. Parallella comes with a Ubuntu-based development kit. The Epiphany architecture features a scalable 2D array with high performance super-scalar RISC processors, a low latency mesh interconnect, and a distributed shared memory subsystem.

This degree project will take an existing run-time system, used in research, and implement and evaluate it for the Parallella platform.

Designing a series of labs for computer architecture course experimenting with architecture

Chisel is a high-level synthesizable design language for FPGAs developed at UC Berkeley. This project is about making sure Chisel works on the infrastructure we have at KTH/ICT and to propose and design a series of laboratory exercises for students in computer architecture.

Evaluation and selection of a soft-core multicore implementation

It is now possible to design multicore processors on large FPGA-chips with several tens of cores. There are several open source efforts being developed all over the world building multicore processors for FPGA:s. In this project, you would try out a couple of these variants and through a requirements analysis select one to implement and evaluate for use in the groups architectural research.

Porting the ArchiDeS Programming System to Parallella

ArchiDeS is a C++-based framework for developing component-based applications with intrinsic data- and pipiline-parallelism and executing them on multicore computs. We use ArchiDeS to build and evaluate executable models of large telecom infrastructure systems. ArchiDeS includes a programming model and a matching C++-based programming environment, and its run-time system incurs minimal CPU and memory-footprint overhead.

Parallella is a power-efficient heterogeneous parallel computer with a 16-core Epiphany processor and ARM A9-based host controller. Parallella comes with a Ubuntu-based development kit. The Epiphany architecture features a scalable 2D array with high performance super-scalar RISC processors, a low latency mesh interconnect, and a distributed shared memory subsystem.

Since individual cores in Epiphany contain a small amount of local memory, an efficient port of ArchiDeS to Parallella needs to be analyzed and optimized for memory footprint.

Contact person: Konstantin Popov at Swedish Institute of Computer Science,

An Extensible Performance Analysis Tool for Dataflow Applications

The Master Degree project aims to develop an extensible performance analysis tool for dataflow applications developed in ArchiDeS - a component-based message-passing programming system for dataflow applications on many-core systems. There is an existing target application - an executable model of physical layer (L1) uplink data processing in LTE (Long-Term Evolution) base stations (eNodeB). L1 uplink processing is irregular due constantly changing baseband resource utilization, pipelined, and the model exhibits a large amount of concurrency - which together makes it difficult to explain and improve the attained performance levels when run on many-core systems such as Tilera 64-core TILEpro.

Contact person: Konstantin Popov at Swedish Institute of Computer Science,

Design, implementation and evaluation of a parameterized task-centric benchmark

[Msc, 1-2 students] Design and implementation of a [synthetic] task-centric benchmark suite, that produces multiprogrammed, unexpected, variable workloads. Currently there are very restricted options, if any, when it comes to any of the above requirements. They could and should be developed for Linux, leaving a port to Barrelfish as optional. This collection of applications should be carefully selected to map to a wide spectrum of real and diverse workloads. Also it has been an open question on how to create a reproducible, multiprogrammed environment.

Benchmarking the difference between message passing and shared memory for the Barrelfish OS

Barrelfish is an operating system designed to enbrace hetrogeneity and distributed memory in contrast to current operating systems for parallel computers which assume a homogeneous architecture using shared memory. We are using the Simics full system simulator as a target platform in our research and our current platform model is a shared memory multiprocessor with cache coherence. The aim of this degree project is to make a distributed memory platform model for Simics and the necssary modifications of Barrelfish to be able to boot on the new platform model. Performance measurments comparing the different models should then be done.

The thesis project is suitable for one or preferably two students and can be performed at both bachelor's and master's level, with different ambitions.